В процессе выполнения программ внутри ЭВМ или во внешней среде могут возникнуть события, требующие немедленной реакции со стороны процессора. Реакция состоит в том, что процессор прерывает обработку текущей программы (прерываемой программы) и переходит к выполнению некоторой другой программы (прерывающей программы), специально предназначенной для данного события. По завершении этой программы процессор возвращается к выполнению прерванной программы. Рассматриваемый процесс называется прерыванием программы и может быть пояснен рис. 6.1.

Каждое событие, требующее прерывания, сопровождается сигналом, оповещающим об этом ЭВМ и называемым запросом прерывания. Прерывания могут порождаться внутренними и внешними событиями:

Внутренние – сбой в аппаратуре, переполнение разрядной сетки, деление на 0, выход из установленной зоны памяти, попытка обратиться к запрещенной зоне памяти, попытка обращения к защищенным программам операционной системы, сигнал от таймера и т.д.

Внешние – запрос от другой ЭВМ, сообщение от аварийных датчиков управляемого технологического процесса, запрос оператора, требование от ПУ операции обмена, запросы на обслуживание клавиатуры, мыши и т.д.

Универсальное приложение для вентиляционных установок | Обзор возможностей

В общем случае запросы прерывания генерируются несколькими, развивающимися параллельно во времени процессами, которые в некоторый момент времени требуют вмешательства процессора. Общим во всех этих запросах является то, что моменты их поступления невозможно предусмотреть. Это существенно отличает процесс прерывания от рассмотренного ранее процесса передачи управления подпрограмме, происходящего в заранее известных точках основной программы.

Возможность прерывания – важное свойство ЭВМ, позволяющее эффективно использовать производительность процессора и прежде всего при организации параллельной работы процессора и периферийных устройств ЭВМ.

Для эффективной организации процесса прерывания и минимизации усилий программиста современные ЭВМ снабжены соответствующими программно-аппаратными средствами, которые получили название контроллера прерываний.

Контроллер прерываний в общем случае является достаточно сложным программируемым устройством, требующим соответствующей инициализации со стороны процессора. В процессе инициализации в управляющие регистры контроллера загружается информация о дисциплине обслуживания запросов прерывания, количестве используемых входов, режиме взаимодействия с процессором и т.д.

Обычно инициализация контроллера выполняется при запуске вычислительной системы. Однако большинство контроллеров прерываний допускают перепрограммирование и в процессе обработки программы, в частности изменение дисциплины обслуживания поступающих запросов прерывания. Конструктивно контроллеры прерываний выполняются в виде отдельных специализированных БИС, но в ряде случаев могут быть встроены в другие устройства вычислительной системы. Простейшие контроллеры прерываний небольших микроЭВМ часто строятся на логических микросхемах общего назначения.

Гиперфокус. Как научиться делать больше, тратя меньше времени | Крис Бэйли

Основными функциями системы прерывания являются:

- запоминание состояния прерываемой программы и осуществление перехода к прерывающей программе;

- восстановление состояния прерванной программы и возврат к ней.

Под термином состояние программы (процессора), строго говоря, следует понимать совокупность состояний всех запоминающих элементов (триггеров, регистров, ячеек памяти) в соответствующий момент времени (например, после выполнения микрокоманды, команды, программы). Однако не вся эта информация искажается при переходе к другой команде или программе, поэтому из всего многообразия информации о состоянии программы (процессора) отбирают наиболее существенные ее элементы, изменяющиеся при переходе к другой команде или программе.

Вектор состояния в каждый момент времени должен содержать информацию, достаточную для запуска программы с точки, соответствующей моменту формирования данного вектора состояния. При этом предполагается, что другая информация о состоянии узлов процессора либо не существенна, либо может быть восстановлена программным путем.

Вектор состояния формируется в соответствующих регистрах процессора, изменяясь после выполнения каждой команды. Наборы информационных элементов, образующих вектор состояния, отличаются у ЭВМ разных типов и зависят от сложности процессора. В простейших процессорах эти наборы невелики. Например, в процессоре КР580ВМ80 (I8080) вектор состояния состоит из содержимого счетчика адреса команд (16 бит), содержимого регистра признаков (8 бит) и содержимого аккумулятора (8 бит). В более сложных процессорах вектор состояния может содержать существенно большее количество элементов.

Аналогично, вектор начального состояния должен содержать всю необходимую информацию для начального запуска программы. Во многих случаях вектор начального состояния содержит только один элемент – начальный адрес запускаемой программы.

При рассмотрении систем прерывания очень широко используется также термин вектор прерывания, который является ничем иным, как вектором начального состояния прерывающей программы (обработчика). Вектор прерывания содержит всю необходимую информацию для перехода к обработчику, в том числе его начальный адрес. Каждому уровню прерываний (см. п. 6.1), а в простых ЭВМ каждому входу прерывания (периферийному устройству) соответствует свой вектор прерывания, который инициализирует выполнение соответствующего обработчика. Обычно векторы прерывания хранятся в специально выделенных фиксированных ячейках памяти с короткими адресами. Таким образом, для перехода к соответствующей прерывающей программе процессор должен располагать не только вектором прерывания, но и адресом этого вектора.

Следует иметь в виду, что понятие вектор прерывания достаточно условно, поскольку в абсолютном большинстве случаев вектор прерывания состоит только из одного элемента – начального адреса прерывающей программы (обработчика).

При наличии нескольких источников запросов должен быть установлен определенный порядок обслуживания поступающих запросов, т.е. должны быть установлены приоритетные соотношения (дисциплина обслуживания). Они определяют, какой из нескольких запросов, поступивших одновременно, подлежит обработке в первую очередь, имеет ли право данный запрос прерывать ту или иную программу и т.д. Все это входит в процедуру перехода к прерывающей программе.

Источник: studfile.net

Система прерываний и приостановок, состояние процессора.

Во время выполнения какой-либо программы компьютером могут возникнуть события, требующие переключения компьютера на другую программу. К ним относятся необходимость незамедлительного решения другой задачи, переполнение разрядной сетки, программный или аппаратный сбой, окончание предусмотренного интервала времени и др.

Запросы на прерывания могут возникать внутри самой ЭВМ и в ее внешней среде.

Внутренние запросы — ошибка в работе аппаратуры, переполнение разрядной сетки, деление на 0, выход из установленной для данной программы области памяти, затребование периферийным устройством операции ввода-вывода, завершение операции ввода-вывода периферийным устройством или возникновение при этой операции особой ситуации и др. Моменты появления запросов на прерывание, как правило, невозможно предусмотреть.

Запросы из внешней среды – это запросы от других ЭВМ, от аварийных и некоторых других датчиков технологического процесса и т.п.

Прерывание может происходить либо по окончании текущей команды, либо по окончании текущего цикла – при высоком приоритете прерывающей программы. В любом случае состояние МП – флаги всех ячеек, состояние регистров запоминаются для последующего восстановления и возобновления работы программы.

Переход к другой программе осуществляется посредством системы прерываний.

Прерывание программы — это процесс переключения процессора с одной программы на другую по внешнему сигналу с сохранением информации для последующего возобновления прерванной программы.

Запрос прерывания – сигнал, формируемый при возникновении события, приводящего к прерыванию. Источники запросов прерывания — это схемы контроля процессора (температура МП и др.), система питания, память, периферийные устройства и т.д. При обслуживании нескольких запросов прерывания им назначаются приоритеты.

Запрос на прерывание запускает программу обслуживания прерывания [ввод данных с клавиатуры, отсутствие места на диске, вывод данных на принтер, проверка Internet-модема и др.]

Состояние машины постоянно фиксируется. Для восстановления работы ЭВМ после прерывания в специальном регистре процессора постоянно находится слово состояния программы, которое и характеризует его состояние. Это слово содержит информацию, необходимую для возобновления программы при прерываниях: указания о разрешенных прерываниях, адрес текущей выполняемой команды, различные признаки, ключи защиты и маски[части кода].

Виды систем прерывания:

1. С помощью регистра запросов прерываний. Запросы прерываний направляются на различные разряды специального регистра — регистра запросов прерываний (РЗП). Его опрос производится в при завершении очередной команды.

В разрядах РЗП записаны приоритеты запросов прерывания, номер разряда определяет приоритет запроса и позволяет найти программу обслуживания прерывания, соответствующую данному запросу. Поступивший запрос может прервать только менее приоритетную программу.

2. Векторная система прерываний. Информация о запросе передается от источника прерываний в виде адреса ячейки памяти, в которой указан адрес перехода к программе обслуживания и дополнительная управляющая информация. Содержимое этой ячейки (или нескольких последовательных ячеек) принято называть вектором прерываний.

3. Приостановка – это остановка работы процессора на цикл занятия памяти. Когда память нужна для процессов приема или выдачи информации, то работа процессора временно останавливается, т.к. память занята. Состояние процессора не меняется, но выполнение очередной команды задерживается до освобождения памяти.

Характеристики системы прерываний:

· общее число входов от источников (число запросов прерываний);

· число уровней прерывания, по которым сгруппированы источники с одной и той же программой прерывания;

· глубина прерывания — это максимальное числом программ, которые могут быть последовательно прерваны друг другом;

· система приоритетов и организация переходов к следующей программе.

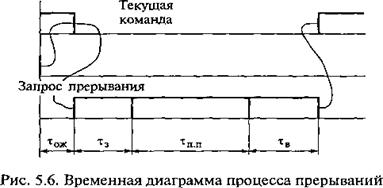

Процесс прерывания состоит из следующих интервалов времени:

1. Время реакции τож — время ожидания, прошедшее между запросом прерывания и началом переключения на программу обслуживания. Зависит от характеристик системы прерывания и от числа ожидающих обслуживания программ со старшими приоритетами. Время реакции определяют для запроса с наибольшим приоритетом, который будет обрабатываться первым. Обычно наивысший приоритет назначают запросам прерываний, поступающим от аппаратуры контроля, чтобы обнаруженная ошибка не оказала влияния на последующую работу компьютера.

В персональных компьютерах, как правило, процесс прерывания происходит по окончании текущей команды (рис. 1), и время реакции определяется длительностью этой команды.

2. Время запоминания параметров текущей команды τ3 (для освобождения ресурсов процессора)

3. Время выполнения прерывающей программы τп.п и

4. Время восстановления параметров текущей программы τв.

В компьютерах для систем реального времени это время может оказаться недопустимо большим, поэтому прерывание выполняется после каждой микрокоманды (из которых состоит команда). При этом количество запоминаемой и восстанавливаемой информации значительно возрастает.

Для уменьшения времени на переключение программ состояние прерванной программы запоминают в специальной стековой памяти. Очевидно, что это время зависит от количества запоминаемой информации.

Время на запоминание параметров текущей программы τ3 и время на восстановление состояния процессора τв определяют длительность переключения программ при прерывании. Эта длительность обычно составляет несколько машинных тактов.

Глубина прерываний — максимальное число программ, способных прерывать друг друга. Более приоритетные запросы обслуживаются в первую очередь. Так, если текущая программа прервана программой ввода-вывода от клавиатуры, а в процессе ее выполнения поступил запрос от накопителя на дисках, то она также будет прервана. После этого завершится программа ввода-вывода от накопителя, затем программа ввода-вывода от клавиатуры, и только после этого – основная программа.

Если запрос на прерывание от какого-либо источника не будет обслужен до прихода очередного запроса от того же источника, то он теряется; возникает насыщение системы прерываний.

Приоритет прерываний. Число различных источников прерывания может достигать нескольких сотен- схемы контроля ЦП, системы питания, памяти, внешние события и т.п.

Все источники подразделяют на отдельные уровни, каждый уровень обрабатывается одной программой обработки прерываний. Запросы (сигналы) поступают на определенные разряды регистра РЗП, устанавливая их в «1».

Поскольку сигналы от источников прерываний могут поступить одновременно, то порядок их обслуживания устанавливается путем назначения приоритетов. Запросы прерываний в зависимости от назначенного приоритета направляются на различные разряды регистра прерываний процессора, опрос которого производится в строго определенной последовательности. Так, запрос самого высокого уровня поступает на первый «опрашиваемый» разряд этого регистра и, следовательно, всегда обрабатывается первым. Самым высоким приоритетом обладают прерывания от схем контроля. Поступивший запрос прерывания может прервать только менее приоритетную программу.

Время задержки в обслуживании прерывания определяется не только реакцией системы, но и числом ожидающих запросов более высокого приоритета.

После обнаружения сигнала прерывания при выполнении каждой команды процессора производится проверка — разрешено ли оно. Если да, то начинается его обслуживание.

Состояние процессора

Понятие состояния процессора (состояния программы) занимает важное место в организации вычислительного процесса в ЭВМ.

Информация о состоянии процессора (программы) лежит в основе многих процедур управления вычислительным процессом, например, анализ ситуаций при отказах и сбоях, при возобновлении выполнения программы после перерывов, вызванных отказами, сбоями, прерываниями, для фиксации состояния процессора (программы) в момент перехода в мультипрограммном режиме от обработки данной программы к другой и т.п.

Состоянием процессора (программы) после данного такта или после выполнения данной команды следует считать совокупность состояний в соответствующий момент времени всех запоминающих элементов устройства – триггеров, регистров, ячеек памяти.

Однако, не вся эта информация исчезает или искажается при переходе к очередной команде или другой программе. Поэтому из всего многообразия информации о состоянии процессора (программы) отбираются наиболее существенные ее элементы, как правило, подверженные изменениям при переходе к другой команде или программе.

Совокупность значений этих информационных элементов получила название векторасостоянияилислова состояния процессора (программы).

Вектор состояния в каждый момент времени должен содержать информацию, достаточную для продолжения выполнения программы или повторного пуска программы с точки, соответствующей моменту формирования вектора состояния. При этом предполагается, что остальная информация, характеризующая состояние процессора, например, содержимое регистров или сохраняется, или может быть восстановлена программным путем по копии, сохраненной в памяти.

Источник: cyberpedia.su

В каждый момент времени должен содержать информацию достаточную для запуска программы с точки

Таким образом, можно сделать следующий вывод. Системы на «жесткой логике» хороши там, где решаемая задача не меняется длительное время, где требуется самое высокое быстродействие, где алгоритмы обработки информации предельно просты. А универсальные, программируемые системы хороши там, где часто меняются решаемые задачи, где высокое быстродействие не слишком важно, где алгоритмы обработки информации сложные.

Автоматическое управление процессом работы микропрограммной ЭВМ по решению задачи достигается на основе принципа программного управления (ППУ), который составляет ее главную особенность и состоит в следующем:

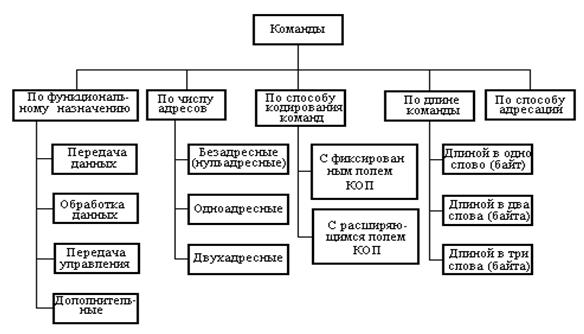

Классификация команд МП

Классификация команд по основным признакам представлена ниже.

По функциональному назначению команды процессора включает в себя следующие основные группы команд:

- Команды передачи (пересылки) данных;

- Команды обработки данных (арифметические, логические);

- Команды передачи управления (переходов);

Команды пересылки данных не требуют выполнения никаких операций над операндами. Даные просто пересылаются (точнее, копируются) из источника (Source) в приемник (Destination). Источником и приемником могут быть внутренние регистры процессора, ячейки памяти или устройства ввода/вывода. АЛУ в данном случае не используется.

Арифметические команды выполняют операции сложения, вычитания, умножения, деления, увеличения на единицу (инкрементирования), уменьшения на единицу (декрементирования) и т.д. Этим командам требуется один или два входных операнда. Формируют команды один выходной операнд.

Логические команды производят над операндами логические операции, например, логическое И, логическое ИЛИ, исключающее ИЛИ, очистку, инверсию, разнообразные сдвиги (вправо, влево, арифметический сдвиг, циклический сдвиг). Этим командам, как и арифметическим, требуется один или два входных операнда, и формируют они один выходной операнд.

Команды переходов предназначены для изменения обычного порядка последовательного выполнения команд. С их помощью организуются переходы на подпрограммы и возвраты из них, всевозможные циклы, ветвления программ, пропуски фрагментов программ и т.д. Команды переходов всегда меняют содержимое счетчика команд. Переходы могут быть условными и безусловными. Именно эти команды позволяют строить сложные алгоритмы обработки информации.

По числу адресов различают однооперандными (или одноадресные) и двухоперандные (или двухадресные).

Команды с регистровой адресацией однобайтовые. Если в команде используется константа в качестве операнда или указывается адрес операнда в системной памяти, то команда будет занимать в системной памяти два или три байта.

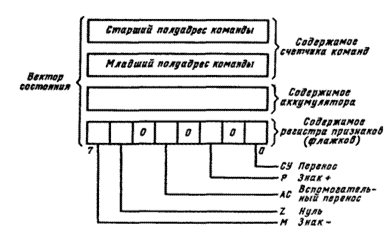

Слово состояния процессора

При выполнении процессором программы после каждого рабочего такта, а тем более в результате завершения выполнения очередной команды, изменяется содержимое регистров, счетчиков, состояния отдельных управляющих триггеров. Можно говорить, что изменяется состояние процессора, или, употребляя другую терминологию, состояние программы.

Информация о состоянии процессора (программы) лежит в основе многих процедур управления вычислительным процессом, например при анализе ситуаций при отказах и сбоях, при возобновлении выполнения программы после перерывов, вызванных отказами, сбоями, прерываниями, для фиксации состояния процессора (программы) в момент перехода в мультипрограммном режиме от обработки данной программы к другой и т. п.. Состоянием процессора (программы) после данного такта или после выполнения данной команды, строго говоря, следует считать совокупность состояний в соответствующий момент времени всех запоминающих элементов устройства — триггеров, регистров, ячеек памяти. Однако не вся эта информация исчезает или искажается при переходе к очередной команде или другой программе. Поэтому из всего многообразия информации о состоянии процессора (программы) отбираются наиболее существенные ее элементы, как правило, подверженные изменениям при переходе к другой команде или программе.

Совокупность значений этих информационных элементов получила название вектора состояния или слова состояния процессора (программы).

Слово состояния процессора (на примере МП К580)

Вектор состояния в каждый момент времени должен содержать информацию, достаточную для продолжения выполнения программы или повторного пуска программы с точки, соответствующей моменту формирования данного вектора состояния. При этом предполагается, что остальная информация, характеризующая состояние процессора, например содержимое регистров, или сохраняется, или может быть восстановлена программным путем по копии, сохраненной в памяти.

Вектор состояния формируется в соответствующем регистре (регистрах) процессора, претерпевая изменения после выполнения каждой команды. Наборы информационных элементов, образующих векторы состояния, отличаются у ЭВМ разных типов. Наиболее просто он выглядит у микропроцессоров. Например, вектор состояния микропроцессора К580, включает в себя содержимое 16-разрядного счетчика команд (адрес очередной команды); содержимое 8-разрядного регистра признаков, называемое в документации на этот микропроцессор словом состояния процессора, и содержимое 8-разрядного аккумулятора АЛУ. Использование слова (вектора) состояния — распространенный прием построения управления устройствами вычислительной техники.

Для нормального функционирования МПС недостаточно управляющих сигналов, формируемых МП на собственных выводах т.к., нельзя отличить циклы обращения к памяти от циклов обращения ввода-вывода.

Расширение числа управляющих сигналов достигается с помощью специального 8-разрядного кода BS (байта состояния), который МП выдает через шину данных в первом такте Т1 каждого машинного цикла. Байт состояния BS содержит информацию о текущем машинном цикле. Таким образом, в каждом машинном цикле МП формирует код типа текущего машинного цикла, который далее декодируется в системном контроллере. В результате декодирования кода типа машинного цикла формируется расширенный набор сигналов шины управления для управления памятью, устройствами ввода-вывода и прерываниями. Всего 11 типов машинных циклов:

1. FETCH Цикл М1 приема первого байта команды в

регистр IR .

2. MEMORY_READ Цикл чтения данных из памяти по адресу,

определяемому PC, BC, DE, HL.

3. MEMORY_WRITE Цикл записи данных в память по адресу,

определяемому BC, DE, HL, SP.

4. STACK-READ Цикл чтения из стека, чтение памяти по адресу, определяемому SP.

5. STACK-WRITE Цикл записи в стек, запись в память по адресу,

6. INPUT Цикл ввода данных из порта в аккумулятор А.

7. OUTPUT Цикл вывода данных из аккумулятора в порт.

8. INTERRUPT-M1 Первый цикл подтверждения прерывания .

9. HALT Цикл останова.

10. HALT-INTERRUPT Первый цикл подтверждения прерываний в

11. INTERRUPT Второй и третий циклы подтверждения прерывания.

Назначение линий управления

F1 и F2 Это входные линии приема взаимно противофазных сигналов тактирования МП. Поступают с генератора тактовых импульсов (рис.2.19).

SYNC Выходная линия, на которую микропроцессор в начале каждого машинного цикла формирует сигнал синхронизации устройств, входящих в систему.

Ready Входная линия приема МП сигнала от ВУ, информирующих о готовности принять или выдать данные (высоким уровнем).

WAIT Выходная линия, на которую МП выставляет сигнал ожидания (высокий уровень), если в такте Т2 отсутствует высокий уровень на линии Ready.

Reset По этой линии поступает сигнал установки МП в исходное состояние. При этом в программный счетчик РС загружается стартовый адрес РС=0000h, с которого начинается пусковая программа. В регистр команд IR записывается код пустой команды NOP, т.е. IR=00h. Внутренние триггеры “разрешение прерывания” и “подтверждение захвата шины” устанавливаются в нулевое состояние.

Состояние РОН и регистра признаков F по сигналу Reset не изменяется.

INT Линия приема сигнала запроса на прерывание от ВУ. МП анализирует состояние этой линии в конце текущей команды или в состояние “Останов”. И если внутренний триггер “разрешения прерываний” установлен в состояние “разрешено” (командой EI), то МП формирует машинные циклы обработки прерывания, выставляя на шину данных байт состояния SB, на основе которого системный контроллер вырабатывает сигналы INTA #.

INTE Выходная линия, на которую МП формирует сигнал

HOLD Входная линия приема сигнала запроса шин, поступающая от ВУ.

HLDA Выходная линия, на которую микропроцессор выставляет сигнал “подтверждение захвата шин” в ответ на сигнал HOLD. При этом буферы на шинах адреса и данных устанавливает в Z-состояние.

DBIN Выходная линия, на которую МП формирует сигнал высокого

уровня при выполнении команд чтения памяти или УВВ.

WR# Выходная линия. При выполнении команд записи в память или

УВВ МП выставляет сигнал низкого уровня.

Генератор тактовых импульсов формирует две взаимно противофазные импульсные последовательности F1 и F2. Микропроцессор воспринимает эти тактирующие сигналы, пересчитывает их с коэффициентом пересчета 3-5. Величина коэффициента пересчета определяется типом выполняемой в данный момент команды.

В начале каждого машинного цикла микропроцессор формирует сигнал синхронизации (SYNC), который поступает на генератор тактовых импульсов. В генераторе тактовых импульсов с приходом сигнала SYNC формируется сигнал STSTB#, служащий для стробирования записи байта состояния SB процессора в регистр системного контроллера. Таким образом, в каждом машинном цикле МП формирует код типа текущего машинного цикла, который далее декодируется в системном контроллере. В результате декодирования кода типа машинного цикла формируется расширенный набор сигналов шины управления для управления памятью, устройствами ввода-вывода и прерываниями. Все сигналы имеют активным низкий уровень:

MEMRD# строб-сигнал чтения памяти.

MEMWR# строб-сигнал записи в память.

IORD# строб-сигнал чтения УВВ (портов).

IOWRC# строб-сигнал записи в УВВ (порты).

INTA# сигнал подтверждения прерывания. Используется для

стробирования чтения адреса подпрограммы обработки прерывания, например из контроллера прерывания КР580ВН59.

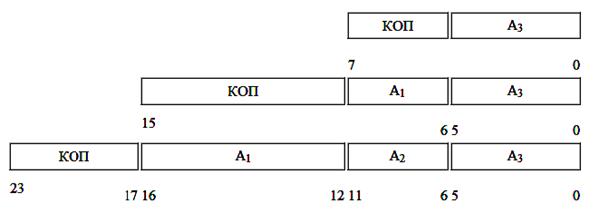

Команды МПС

Алгоритм, написанный пользователем программы, реализуется в виде машинных команд. Под командой понимают совокупность сведений, представленных в виде двоичных кодов, необходимых процессору для выполнения очередного шага. В коде команды для хранения сведений о типе операции, нахождении обрабатываемых данных и месте хранения результатов выделяются определенные разряды (поля).

|

Рис 2.5. Формат команды

Форматом команды называется заранее обговоренная структура полей в её кодах, позволяющая ЭВМ распознавать составные части кода.

Главным элементом кода команды является код операции (КОП), он определяет, какие действия будут выполнены по данной команде. Под него выделяется N старших разрядов формата. В остальных разрядах размещаются А1 и А2 — адреса операндов. А3 — адрес результата.

Длина команды зависит от числа адресных полей. По числу адресов команды делятся на:

— одно-, двух-, трехадресные.

Длина кода команды измеряется в машинных словах.

Чтобы минимизировать число адресных полей, результат можно размещать по месту хранения одного из операндов (ADD AX, BX). Либо предварительно размещать один или несколько операндов в специально выделенных регистрах процессора (аккумуляторах). Также во многих типах операций (например, логических) третий, а часто и второй адрес вообще не используется (RET, IRET, JE xx, INC AL). Оттранслированные команды записываются в соседние ячейки памяти в порядке их следования в программе.

Множество реализуемых операций машины образует её систему команд. Система команд часто определяет области и эффективность применения ЭВМ. К системе команд ЭВМ предъявляют требования минимальности и функциональной полноты. Большинство алгоритмов может быть реализовано небольшим базовым набором команд. Вместе с тем система команд должна быть полной, т.е. содержать все команды, которые необходимы для интерпретации алгоритма в машинных кодах.

Принципы работы ЭВМ по структуре фон Неймана

Принципы работы ЭВМ иллюстрируются на рис. 2.6. По адресу команды, которая определяется содержимым СчК, выбирается из соответствующей ячейки ОЗУ слово, представляющее собой очередную команду программы и пересылается в регистр команд РгК. Часть команды (код операции) направляется в дешифратор ДШ.

После чего, в соответствии с КОП формируется требуемая последовательность управляющих импульсов, которая подается на те устройства, которые должны выполнять расшифрованную операцию. Если КОП относится к арифметическим или логическим операциям, эти импульсы поступают в АУ.

По адресной части команды (А1 – А3) УУ вырабатывает сигналы управления для ОЗУ, обеспечивающие чтение операндов по адресам А1 и А2, посылку их в АУ и запись результатов по третьему адресу А3 обратно в ОЗУ. Признаки результата (знак, наличие переполнения, признак нуля и так далее) поступают в УУ, где записываются в специальный регистр признаков (РП).

После завершения выполнения данной операции, что определяется регистром состояния, в СчК добавляется единица (+1) и в следующем такте из ОЗУ будет выбрана следующая команда программы по порядку номеров ячеек ОЗУ, и затем этот процесс будет повторяться.

Эта последовательность может быть нарушена лишь в том случае, когда в ходе вычислительного процесса появляется необходимость повторить участок программы или перейти, не выполняя, полностью какую-то часть программы. В этом случае специальной командой управления в СчК заносится не увеличенной на 1 адрес ячейки, а адрес ячейки, указанный в управляющей команде. Последовательность выборки команд при этом изменяется и начинается с указанной ячейки.

Дата: 2018-12-28, просмотров: 513.

Источник: findout.su