Выборка программы из памяти осуществляется с помощью счетчика команд. Этот регистр процессора последовательно увеличивает хранимый в нем адрес очередной команды на длину команды.

А так как команды программы расположены в памяти друг за другом, то тем самым организуется выборка цепочки команд из последовательно расположенных ячеек памяти.

Если же нужно после выполнения команды перейти не к следующей, а к какой-то другой, используются команды условного или безусловного переходов, которые заносят в счетчик команд номер ячейки памяти, содержащей следующую команду. Выборка команд из памяти прекращается после достижения и выполнения команды “стоп”.

Таким образом, процессор исполняет программу автоматически, без вмешательства человека.

2. Принцип однородности памяти. Программы и данные хранятся в одной и той же памяти. Поэтому компьютер не различает, что хранится в данной ячейке памяти — число, текст или команда. Над командами можно выполнять такие же действия, как и над данными.

hw

Это открывает целый ряд возможностей. Например, программа в процессе своего выполнения также может подвергаться переработке, что позволяет задавать в самой программе правила получения некоторых ее частей (так в программе организуется выполнение циклов и подпрограмм).

Более того, команды одной программы могут быть получены как результаты исполнения другой программы. На этом принципе основаны методы трансляции — перевода текста программы с языка программирования высокого уровня на язык конкретной машины.

3. Принцип адресности. Структурно основная память состоит из перенумерованных ячеек; процессору в произвольный момент времени доступна любая ячейка.

Отсюда следует возможность давать имена областям памяти, так, чтобы к запомненным в них значениям можно было впоследствии обращаться или менять их в процессе выполнения программ с использованием присвоенных имен.

Компьютеры, построенные на этих принципах, относятся к типу фон-неймановских.

Но существуют компьютеры, принципиально отличающиеся от фон-неймановских. Для них, например, может не выполняться принцип программного управления, т.е. они могут работать без “счетчика команд”, указывающего текущую выполняемую команду программы. Для обращения к какой-либо переменной, хранящейся в памяти, этим компьютерам не обязательно давать ей имя. Такие компьютеры называются не-фон-неймановскими.

Вернемся к понятию команды и проследим их выполнение в компьютере.

Команда — это описание элементарной операции, которую должен выполнить компьютер

В общем случае, команда содержит следующую информацию:

Источник: studfile.net

Принцип программного управления. Программа состоит из набора команд, выполняющихся процессором автоматически в определенной последовательности

Программа состоит из набора команд, выполняющихся процессором автоматически в определенной последовательности.

archos1

Вначале с помощью какого-либо внешнего устройства в память компьютера вводится программа. Устройство управления считывает содержимое ячейки памяти, где находится первая инструкция (команда) программы, и организует ее выполнение.

Эта команда может задавать выполнение арифметических или логических действий, чтение из памяти данных для выполнения арифметических или логических операций или запись их результатов в память, ввод данных из внешнего устройства в память или вывод данных из памяти на внешнее устройство.

Выборка программы из памяти осуществляется с помощью счетчика команд. Этот регистр процессора последовательно увеличивает хранимый в нем адрес очередной команды на длину команды. Так как команды расположены в памяти друг за другом, организуется выборка цепочки команд из последовательно распложенных ячеек памяти.

Если же нужно после выполнения команды перейти не к следующей, а к какой-то другой ячейке, то используются команды условного и безусловного перехода, которые заносят в счетчик команд номер ячейки памяти, содержащей следующую команду. Выборка команд из памяти прекращается после достижения и выполнения команды «стоп». Процессор исполняет программу автоматически, без вмешательства человека.

Принцип программного управления обеспечивает универсальность использования компьютера: в определенный момент времени решается задача по соответственно выбранной программе. После ее завершения в память загружается другая программа и т.д.

Принцип однородности памяти

Программы и данные хранятся в одной и той же памяти, поэтому компьютер не различает, что хранится в данной ячейке памяти — число, текст или команда. Над командами можно выполнять такие же действия, как и над данными.

Понравилась статья? Добавь ее в закладку (CTRL+D) и не забудь поделиться с друзьями:

Источник: studopedia.ru

Основные архитектурные принципы построения компьютера. Компьютер фон Неймана. Узкие места компьютера фон Неймана и его усовершенствования.

Таким образом, характерной чертой компьютеров фон Неймана является наличие глобально адресуемой памяти и счетчика команд, которые позволяют УУ многократно повторять один и тот же цикл действий:

- извлечение очередной команды машинного кода,

- декодирование и выполнение команды

в автоматическом режиме. В результате глобально адресуемая память и счетчик команд создают поток команд, которые УУ декодирует, а АЛУ исполняют.

Управляющие стратегии вычислений

• Команда выполняется, если предыдущая команда, определенная в машинном коде, выполнена (control flow).

• Команда выполняется, когда требуемые операнды готовы (data flow).

• Команда выполняется, когда ее результат требуется другой команде (demand driven).

• Команда выполняется, когда появляются частичные образы данных (pattern driven).

Узкие места архитектуры фон Неймана

• Последовательное выполнение команд

• Хранение данных и программы в одном ОЗУ

• Один канал связи

Архитектурные усовершенствования

Оптимизация подсистемы памяти

• Кэш и иерархия памяти

• Аппаратная предвыборка данных и команд

Оптимизация выполнения команд

• Упрощение набора команд

Иерархия памяти. Основной принцип построения иерархической памяти. Типичная схема иерархии памяти.

Идея иерархической (многоуровневой) организации памяти заключается в использовании на одном компьютере нескольких уровней памяти, которые характеризуются разным временем доступа к памяти и объемом памяти. (Время доступа к памяти это время между операциями чтения/записи, которые выполняются по случайным адресам.) Основой для иерархической организации памяти служит принцип локальности ссылок во времени и в пространстве.

• Локальность во времени состоит в том, что процессор многократно использует одни и те же команды и данные.

• Локальность в пространстве состоит в том, что если программе нужен доступ к слову с адресом A, то скорее всего, следующие ссылки будут к адресам, расположенным по близости с адресом A.

Из свойства локальности ссылок следует, что в типичном вычислении обращения к памяти концентрируются вокруг небольшой области адресного пространства и более того, выборка идет по последовательным адресам. Время доступа к иерархически организованной памяти уменьшается благодаря следующему

• сокращению количества обращений к оперативной памяти

• совмещению обработки текущего фрагмента программы и пересылки данных из основной памяти в буферную память.

- Регистровая память – 1 такт

- Кэш 1-го уровня – 1-2 такта

- Кэш 2-го уровня – 3-5 тактов

- Кэш 3-го уровня – 6-11 тактов

- Основная память – 12-55 тактов

- Внешняя память — 10 6 тактов

интерливингом — расслоением адресов ячеек памяти — весь объем памяти делится на несколько банков. Двойные слова с последовательными адресами располагаются в разных банках. Во время считывания информации из оперативной памяти за один цикл можно организовать параллельное извлечение информации из разных блоков, что уменьшает количество циклов ожидания.

Схема построения кэш-памяти

• Кэш-память построена на принципе локальности ссылок во времени и в пространстве.

• Кэш-контроллер загружает копии программного кода и данных из ОП в кэш-память блоками, равными размеру строки за один цикл чтения. Процессор читает из кэш-памяти по словам.

• Кэш-контроллер перехватывает запросы процессора к основной памяти и проверяет, есть ли действительная копия информации в кэш-памяти.

Запрос на чтение

М в М (R1): запрос на чтение приводит к кэш-попаданию, данные находятся в кэш-памяти и передаются в процессор.

Е в Е (R2): как и в предыдущем случае, запрос на чтение приводит к кэш-попаданию, данные находятся в кэш-памяти и передаются в процессор.

S в S (R3): запрос на чтение приводит к кэш-попаданию, данные находятся в кэш-памяти и передаются в процессор.

I в E (R4): запрос на чтение приводит к кэш-промаху, данных в кэш-памяти нет. Кэш-контроллер запускает внешний цикл чтения для того, чтобы прочитать информацию и переходит в эксклюзивное состояние

I в S (R5): как и в предыдущем случае

I в I (R6): запрос на чтение приводит к кэш-промаху, данных в кэш-памяти нет. Однако заполнение кэш-строки не может быть выполнено кэш-контроллером. Таким образом, строка остается недействительной.

Запрос на запись

М в М (W1): запрос на запись приводит к кэш-попаданию, данные находятся в кэш-памяти и перезаписываются. Это соответствует стратегии кэш-памяти с отложенной записью

Е в М (W2): запрос на запись приводит к кэш-попаданию. Кэш-контроллер перезаписывает кэш-строку и отмечает ее как модифицированную. Этот случай также соответствует стратегии кэш-памяти с отложенной записью.

S в E (W3): запрос на запись приводит к кэш-попаданию. Поскольку исходная строка помечена как разделяемая, она может храниться и в других кэш-блоках. Согласно протоколу MESI, этот элемент должен быть объявлен недействительным, и кэш-контроллер поэтому запускает цикл записи через внешнюю шину. Таким образом, после этого строка будет находиться только в локальной кэш-памяти; в соответствии с циклом сквозной записи, элемент в основной памяти также обновляется. После этого кэш-строка объявляется эксклюзивной.

S в S (W4): в этом случае запрос на запись тоже приводит к кэш-попаданию. Однако W4 соответствует стратегии кэш-памяти со сквозной записью. По этой причине все последующие запросы на запись передаются на шину, что обеспечивает соблюдение стратегии сквозной записи; кэш-строка остается помеченной как разделяемая.

I в I (W5): запрос на запись приводит к кэш-промаху, данных в кэш-памяти нет. Нужный отсутствующий элемент данных из основной памяти в кэш-память не загружается. Кэш-строка остается недействительной.

Просмотр

M в S (S1): цикл проверки обнаруживает модифицированную кэш-строку, поэтому недействительной она не объявляется. Соответствующая кэш-строка перезаписывается в основную память.

M в I (S2): цикл проверки обнаруживает модифицированную кэш-строку; на этот раз она объявляется недействительной. Соответствующая кэш-строка перезаписывается в основную память.

E в S (S3): цикл проверки обнаруживает кэш-строку, помеченную как эксклюзивная. Она не изменялась и поэтому не должна перезаписываться в основную память. Эта операция служит для пересылки строки, которая вначале находилась только в одной кэш-памяти, во вторую.

E в I (S4): в цикле проверки была обнаружена кэш-строка, помеченная как эксклюзивная. Она не изменялась, поэтому ее также не надо перезаписывать в основную память. В противоположность предыдущему случаю, кэш-строка должна быть объявлена недействительной,

S в S (S5): в цикле проверки была обнаружена кэш-строка, помеченная как разделяемая.

S в I (S6): в цикле проверки была обнаружена кэш-строка, помеченная как разделяемая. Она не изменялась и поэтому не должна перезаписываться в основную память при последующем объявлении ее недействительной.

I в I (S7): в цикле проверки была обнаружена кэш-строка, помеченная как недействительная, т.е. не содержащая достоверной информации.

DLP

• Векторные вычисления (SIMD) – SIMD

расширения были введены в архитектуру x86 с целью повышения скорости обработки потоковых данных. Основная идея заключается в одновременной обработке нескольких элементов данных за одну инструкцию.

• Единообразная обработка массивов данных

Pentiumы II, III, IV

ILP-процессоры

• Имеют несколько исполнительных устройств

• Исполняют несколько команд одновременно

TLP

Многопоточность – это свойство платформы или программы, позволяющее процессу состоять из нескольких потоков команд, исполняющихся параллельно, без предписанного порядка во времени.

Крупнозернистая многопоточность (Coarse-grained MT)

• 2 и более аппаратных контекстов

– Регистры общего назначения

– Буфер выборки инструкций

• Одновременно не более 1 нити

• Аппаратное переключение контекстов при прерывании

Мелкозернистая многопоточность (Fine-grained MT)

• 2 и более аппаратных контекстов

– Регистры общего назначения

• Одновременно не более 1 нити

• Аппаратное переключение на каждом такте

Одновременная многопоточность (Simultaneous MT)

• 2 и более аппаратных контекстов

– Регистры общего назначения

– Буфер выборки инструкций

• Привязка команд и нитей

• До нескольких нитей одновременно

• Контексты активны, переключения не происходит

CMP

SMT

ILP-процессоры

• Имеют несколько исполнительных устройств

• Исполняют несколько команд одновременно

Суперскалярные

• Меньше ресурсов процессора

• Меньше команд за такт: 3, 4, 5 (<50%)

VLIW / EPIC

• Больше ресурсов процессора

• Больше команд за такт: 6 (>50%)

Itanium2 Эльбрус 2000 – VLIW/EPIC

Alpha Power – RISC суперскаляр

Параллелизм данных

Основная идея подхода, основанного на параллелизме данных, заключается в том, что одна операция выполняется сразу над всеми элементами массива данных. Различные фрагменты такого массива обрабатываются на векторном процессоре или на разных процессорах параллельной машины. Распределением данных между процессорами занимается программа. Векторизация или распараллеливание в этом случае чаще всего выполняется уже на этапе компиляции – перевода исходного текста программы в машинные команды. Роль программиста в этом случае обычно сводится к заданию опций векторной или параллельной оптимизации компилятору, директив параллельной компиляции, использованию специализированных языков для параллельных вычислений.

• Векторные вычисления (SIMD)

• Единообразная обработка массивов данных

SIMD-расширения были введены в архитектуру x86 с целью повышения скорости обработки потоковых данных. Основная идея заключается в одновременной обработке нескольких элементов данных за одну инструкцию.

– x86: MMX, 3DNow!, SSE, SSE2, …

• Перспективные векторные процессоры

Первой SIMD-расширение ввела фирма Intel — это расширение MMX. Оно стало использоваться в процессорах Pentium MMX и Pentium II. Расширение MMX работает с 64-битными регистрами MM0-MM7, физически расположенными на регистрах сопроцессора, и включает 57 новых инструкций для работы с ними. 64-битные регистры логически могут представляться как одно 64-битное, два 32-битных, четыре 16-битных или восемь 8-битных упакованных целых

Расширение 3DNow! — Технология 3DNow! была введена фирмой AMD в процессорах K6. Расширение работает с регистрами 64-битными MMX, которые представляются как два 32-битных вещественных числа с одинарной точностью. Система команд расширена 21 новой инструкцией, среди которых есть команда выборки данных в кэш L1.

Расширение SSE

С процессором Intel Pentium III впервые появилось расширение SSE. Это расширение работает с независимым блоком из восьми 128-битных регистров XMM0-XMM7. Каждый регистр XMM представляет собой четыре упакованных 32-битных вещественных числа с одинарной точностью. Команды блока XMM позволяют выполнять как векторные, так и скалярные операции. Кроме инструкций с блоком XMM в расширение SSE входят и дополнительные целочисленные инструкции с регистрами MMX, а также инструкции управления кэшированием.

Расширение SSE2

В процессоре Intel Pentium 4 набор инструкций получил очередное расширение — SSE2. Оно позволяет работать с 128-битными регистрами XMM как с парой упакованных 64-битных вещественных чисел двойной точности, а также с упакованными целыми числами: 16 байт, 8 слов, 4 двойных слова или 2 учетверенных (64-битных) слова. Введены новые инструкции вещественной арифметики двойной точности, инструкции целочисленной арифметики, 128-разрядные для регистров XMM и 64-разрядные для регистров MMX. Ряд старых инструкций MMX распространили и на XMM (в 128-битном варианте).

Недостатки

- Долгое время планирования потока команд.

- Невозможность учесть динамику исполнения программы.

Примеров данной архитектуры является Itanium

Явный ILP (параллелизм на уровне команд)

- Компилятор объединяет команды процессора в связки по три, которые могут быть

- Процессор обеспечивает большое число ресурсов для реализации ILP.

Способы увеличения ILP

- Явная спекуляция по данным и управлению (уменьшает задержки по памяти).

- Предикатное исполнение команд (устраняет ветвления).

- Аппаратная поддержка программной конвейеризации циклов.

- Предсказание ветвлений.

Простой широкий конвейер

- Много команд за такт (до 6)

Способы увеличения ILP

- Явная спекуляция по данным и управлению (уменьшает задержки по памяти).

- Предикатное исполнение команд (устраняет ветвления).

- Аппаратная поддержка программной конвейеризации циклов.

- Предсказание ветвлений.

Простой широкий конвейер

- Много команд за такт (до 6)

CMP

SMT

CMP + SMT

Основные архитектурные принципы построения компьютера. Компьютер фон Неймана. Узкие места компьютера фон Неймана и его усовершенствования.

Основные принципы компьютера Фон Неймана:

- Принцип использования двоичной системы счисления для представления данных и команд.

- Принцип программного управления. — Программа состоит из набора команд, которые выполняются процессором друг за другом в определенной последовательности.

- Принцип однородности памяти. — Как программы (команды), так и данные хранятся в одной и той же памяти (и кодируются в одной и той же системе счисления — чаще всего двоичной). Над командами можно выполнять такие же действия, как и над данными.

- Принцип адресуемости памяти. — Структурно основная память состоит из пронумерованных ячеек; процессору в произвольный момент времени доступна любая ячейка.

- Принцип последовательного программного управления — Все команды располагаются в памяти и выполняются последовательно, одна после завершения другой.

- Принцип условного перехода.

Таким образом, характерной чертой компьютеров фон Неймана является наличие глобально адресуемой памяти и счетчика команд, которые позволяют УУ многократно повторять один и тот же цикл действий:

- извлечение очередной команды машинного кода,

- декодирование и выполнение команды

в автоматическом режиме. В результате глобально адресуемая память и счетчик команд создают поток команд, которые УУ декодирует, а АЛУ исполняют.

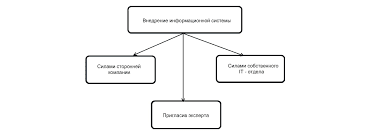

Что делает отдел по эксплуатации и сопровождению ИС? Отвечает за сохранность данных (расписания копирования, копирование и пр.).

ЧТО ПРОИСХОДИТ ВО ВЗРОСЛОЙ ЖИЗНИ? Если вы все еще «неправильно» связаны с матерью, вы избегаете отделения и независимого взрослого существования.

Система охраняемых территорий в США Изучение особо охраняемых природных территорий(ООПТ) США представляет особый интерес по многим причинам.

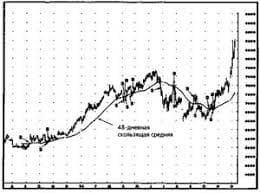

Что вызывает тренды на фондовых и товарных рынках Объяснение теории грузового поезда Первые 17 лет моих рыночных исследований сводились к попыткам вычислить, когда этот.

Не нашли то, что искали? Воспользуйтесь поиском гугл на сайте:

Источник: zdamsam.ru