Одна из глав книги «Код» Чарльза Петцольда посвящена проектированию блоков CPU и в начале главы описывается устройство, позволяющие суммировать наборы чисел, хранящихся в памяти. Спроектируем похожую схему в Logisim.

Возьмем набор восьмиразрядных чисел и подключим его к мультиплексору, переход от одного числа к другому будем осуществлять с помощью счетчика, подключенного к выбирающему входу мультиплексора, а к выходу мультиплексора подключим сумматор и аккумулятор. В качестве тактового генератора будем использовать кнопку. Данные будут загружаться в аккумулятор при отпускании кнопки. Это осуществляется с помощью элемента НЕ, подключенного к кнопке. Про реализацию этих функциональных блоков в виде отдельных микросхем далее в статье.

Будем хранить числа в ОЗУ (RAM).

ОЗУ можно представить в виде набора регистров, доступ к которым производится с помощью демультиплексора и мультиплексора (DMX и MUX).

Гарвардская архитектура

Предположим, в ОЗУ хранится набор чисел, а нам нужно сложить все числа и сохранить результат (в свободную ячейку). Будем хранить команды («сложить» и «сохранить») в одном ОЗУ, а обрабатываемые числа — в другом. Такой способ хранения является отличительным признаком Гарвардской архитектуры.

Функция Logisim о которой не говорят -Комбинационный анализ!

Команда «1» будет записывать число из сумматора в аккумулятор, команда «2» будет записывать число из аккумулятора во 2-ое ОЗУ.

- загружать числа из ОЗУ в аккумулятор

- загружать числа из сумматора в аккумулятор

- сохранять числа из аккумулятора в ОЗУ

Архитектура фон Неймана

Далее, будем хранить инструкции и данные в одном ОЗУ. Такой способ хранения является отличительным признаком архитектуры фон Неймана.

В первых четырех разрядах восьмиразрядной ячейки памяти будет храниться команда, во вторых четырех разрядах будет храниться адрес (прямая адресация).

Будем загружать адрес и команду в отдельные регистры, а затем с помощью мультиплексора переходить по сохраненному адресу. Для записи данных в ОЗУ будем сначала загружать данные во временный регистр Temp (иначе в ОЗУ запишутся инструкции, а не данные), а потом в аккумулятор Асс. Запись данных в Temp и Асс будем производить по заднему фронту.

Будем складывать, например, числа 2 и 3, которые лежат в ячейках 8 и 9, а сохранять результат в ячейку с адресом a.

Добавим также возможность совершать безусловные переходы.

Реализуем устройство, в котором будет выполняться всего одна команда — команда безусловного перехода. Для этого на счетчик, генерирующий адрес, будем отправлять четыре младших разряда (собственно, адрес), а на порт загрузки будем подавать команду, хранящуюся в старших разрядах ячейки памяти.

Например, для прыжка в ячейку с адресом 2 используется команда 82.

Добавим команду безусловного перехода в предыдущую схему.

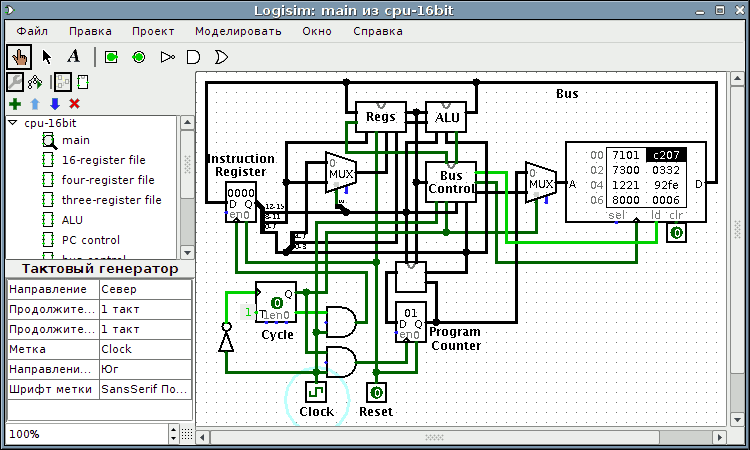

Вообще, на geektimes уже была статья, посвященная проектированию CPU в Logisim.

Все схемы, представленные выше, можно скачать одним файлом.

Вебинар «Проектирование цифровых электронных схем в Logisim»

Logisim можно скачать здесь.

Терминал

Добавим к схеме терминал для демонстрации того, как ассемблерные инструкции преобразуются в машинный код.

Добавим конечный автомат для обработки последовательностей поступающих символов.

Семизначный код буквы «i» равняется 1101001

Семизначный код буквы «n» равняется 1101110

Семизначный код буквы «p» равняется 1110000

Для выделения конкретной буквы из потока символов будем использовать компаратор. В начальном состоянии компаратор сравнивает поступивший символ с семизначным кодом буквы «i»

Автомат переходит в следующее состояние, если после буквы «i» поступает буква «n»

Автомат переходит в следующее состояние, если после букы «i», а затем «n» поступает буква «p»

Добавим команду out

Подробнее о командах inp и out можно прочитать в следующей части.

Железо

Рассмотрим, как работает сумматор на примере микросхемы 155им3 (7483). Для микросхем 155-й серии условимся, что на входах есть внутренний резистор, подтягивающий к плюсу (если ножка «висит в воздухе», то на ней присутствует логическая «единица»), поэтому при подключении питания к микросхеме зажгутся все светодиоды, присоединенные к выходу.

На картинке представлена МС 74ls283 (современный аналог 155им3).

Для того, чтобы в Logisim спроектировать такую микросхему, необходимо выбрать «Меню» — «Проект» — «Добавить схему».

Вот как эта МС выглядит внутри подсхемы. Это четыре полусумматора, объединённые в полный сумматор.

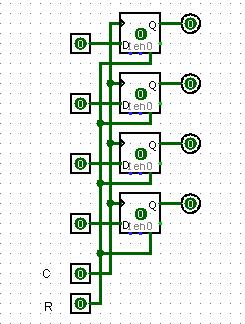

В качестве аккумулятора будем использовать микросхему 155тм8 (74175) — счетверённый D-триггер.

Триггеры, входящие в состав МС, пропускают насквозь всё время, пока на входе синхронизации присутствует 1, а не только по фронту (триггеры со статическим управлением), но в программе Logisim нам доступны только триггеры с динамическим управлением, но в данном случае это не важно; будем использовать то, что есть.

Подробнее про триггеры можно прочитать в Википедии.

Соберём из D-триггеров модель МС 155тм8.

Далее соберём схему, позволяющую складывать наборы чисел.

Например, если сложить набор из чисел 2 (0010), мы получим 2 (0010), 4 (0100), 6 (0110) и т.д.

Сперва 2 появляется на выходе сумматора (красные светодиоды), затем 2 загружается в счетверенный D-тригер (желтые светодиоды), а на выходе сумматора появляется 4, затем 4 загружается в 155тм8, а на выходе сумматора появляется 6 и т.д.

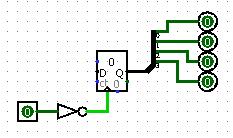

Для того, чтобы спроектировать простой модуль памяти, нам понадобится мультиплексор. Спроектируем сдвоенный мультиплексор 155кп2.

Также нам понадобится счетчик. Спроектируем микросхему 155ие5.

Это четырехразрядный счетчик, но нам понадобится только два младших разряда.

Будем хранить числа, например, 2 (0010), 3 (0011), 5 (0101).

Объединим все компоненты в одну схему. Будем складывать числа, которые хранятся в «памяти»

2 + 3 + 5.

P.S. Статья про книгу «Код. Тайный язык информатики.» есть на Хабре вот здесь.

З.Ы. Переводные статьи (автор переводов PatientZero) про архитектуру процессора здесь, здесь и здесь

- cpu design

- logisim

- тайный язык информатики

- Схемотехника

- DIY или Сделай сам

- Электроника для начинающих

Источник: habr.com

3. Изучение программы моделирования Logisim

3.4. Порядок выполнения задания

Задание выполняется каждым учащимся индивидуально. Результаты заданий лабораторного практикума и соответствующих заданий практикума должны совпадать. Отчёт формируется в электронном виде в формате PDF и отправляется на электронную почту преподавателя. 3.4.1.

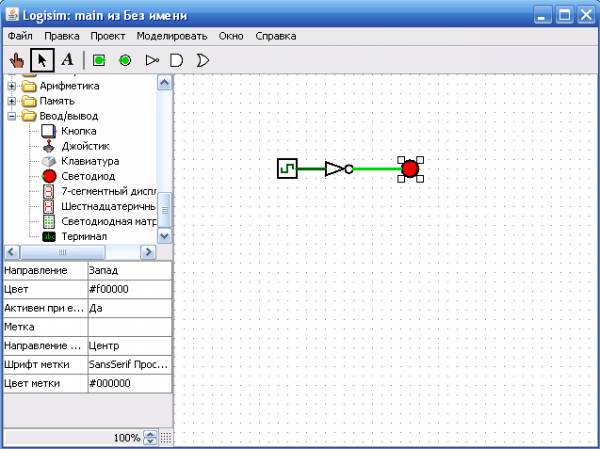

Построение простейшей схемы «Логическое И» Построить простейшую схему, состоящую из двух входов, элемента «Логическое И» (AND) и выхода (рис. 3.1 ). Научиться смотреть таблицу истинности схемы. При выполнении задания рекомендуется использовать встроенную справку Logisim раздел «Пособие начинающего». Рис. 3.1. Схема «Логическое И»

1. Разместить на холсте два входных контакта (квадратные), выходной контакт (круглый) и логический элемент AND по образцу рис. 3.1 . Эти элементы вынесены на панель инструментов программы. В свойствах контактов задать их имена (метки) по образцу рис.

3.1 . 2. Использовав инструмент «Рука» из панели инструментов, изменять значения входных контактов и следить, как меняется значение на выходном контакте. Сравнить с таблицей истинности элемента AND. 3. Просмотреть таблицу истинности построенной схемы, использовав пункт главного меню «Проект» – «Анализировать схему» – вкладка «Таблица». Сверить с таблицей из пособия. 3.4.2.

Построение одноразрядного полусумматора Построить одноразрядный полусумматор на основе базовых логических элементов и на основе элементов XOR (рис. 3.2 ), использовав один набор входов для обеих схем. Научиться использовать тоннели. Рис. 3.2. Варианты схемы одноразрядного полусумматора 1. Построить схему по образцу рис. 3.2 . В свойствах контактов задать соответствующие метки.

Входные контакты подключить к тоннелям («Проводка» — «Тоннель»). Направление и метка тоннеля и задаются в его свойствах. 2. Использовав инструмент «Рука» из панели инструментов, изменять значения входных контактов и следить, как меняется значение на выходных контактах. Убедиться, что контакты «s1»/«s2» и «po1»/«po2» показывают равные значения.

Сравнить с таблицей истинности одноразрядного полусумматора. 3. Просмотреть таблицу истинности построенной схемы, использовав пункт главного меню «Проект» – «Анализировать схему» – вкладка «Таблица». При появлении предупреждения «Выражение неопределно» нажать кнопку «OK». Сверить с таблицей из пособия.

3.4.3. Построение линии задержки и блоков ввода и вывода Построить линию задержки на одноразрядных регистрах (рис. 3.3 ). Научиться создавать входной сдвиговый регистр для записи в него начальных значений и выходной сдвиговый регистр для просмотра результата. Рис. 3.3. Схема линии задержки на 7 тактов 1. Построить схему по образцу рис.

3.3 . Входной и выходной регистры должны иметь разрядность («Биты данных»), равную 1, и длину («Количество ступеней») 16. В свойствах регистров, формирующих линию задержки, указать разрядность («Биты данных»), равную 1. На центральный западный вход входного сдвигового регистра подать однобитовую константу «0». «Бит записи» исходно должен быть равен 0. 2. Использовав инструмент «Рука» из панели инструментов, задать начальные данные для записи во входной регистр.

3. Установить «Бит записи» в «1». Затем однократно нажать кнопку «Такты». Убедиться, что входной регистр проинициализировался. Установить «Бит записи» в «0». 4. Последовательным нажатием кнопки «Такты» передавать биты из входного регистра в линию задержки и далее в выходной регистр. Убедиться, что линия действительно вносит задержку в 7 тактов.

5. Обнулить выходной регистр нажатием соответствующей кнопки. 3.4.4. Построение линии задержки с внесением помехи Построить линию задержки с внесением помехи (рис. 3.4 ). Рис. 3.4. Схема линии задержки на 7 тактов с внесением помехи

1. Построить схему по образцу рис. 3.4 . Генератор случайных чисел, играющий роль источника помех, должен иметь разрядность, равную 1. Стоит отметить, что такая схема аналогична двоичному симметричному каналу с вероятностью битовой ошибки 0;5. 2. Использовав инструмент «Рука» из панели инструментов, задать начальные данные для записи во входной регистр. 3. Установить «Бит записи» в «1».

Затем однократно нажать кнопку «Такты». Убедиться, что входной регистр проинициализировался. Установить «Бит записи» в «0». 4. Последовательным нажатием кнопки «Такты» передавать биты из входного регистра в линию задержки и далее в выходной регистр (всего 23 такта). Сравнить полученный результат с исходными данными.

5. Обнулить выходной регистр и регистры линии задержки нажатием соответствующей кнопки.

3.5. Порядок защиты практической работы

Защита работы может осуществляться одним из нижеперечисленных способов или их сочетанием на усмотрение преподавателя. 1. Устный ответ по теме работы. 2. Тестирование по теме работы 3. Задача по теме работы. 4. Иные варианты на усмотрение преподавателя.

Источник: studfile.net

Как запустить тестирование схемы в logisim

3.1. цель работы изучить общие принципы работы с системой моделирования logisim. 3.2.рекомендуемая литература 1.logisim: документация // официальный сайт logisim. url:

3.1. Цель работы

Изучить общие принципы работы с системой моделирования Logisim.

3.2. Рекомендуемая литература

1. Logisim: Документация // Официальный сайт Logisim. URL: http://www.cburch.com/logisim/ru/docs.html

3.3. Теоретическая справка

Справка написана для версии программы из репозитория ОС Debian Linux, использующейся в лабораториях кафедры.

3.3.1. Запуск системы Logisim

Программа Logisim запускается через пункт главного меню «Logisim» либо соответствующей командой в терминале.

Команда для вызова Logisim

3.4. Порядок выполнения задания

Задание выполняется каждым учащимся индивидуально. Результаты заданий лабораторного практикума и соответствующих заданий практикума должны совпадать.

Отчёт формируется в электронном виде в формате PDF и отправляется на электронную почту преподавателя.

3.4.1. Построение простейшей схемы «Логическое И»

Построить простейшую схему, состоящую из двух входов, элемента «Логическое И» (AND) и выхода (рис. 3.1 ). Научиться смотреть таблицу истинности схемы. При выполнении задания рекомендуется использовать встроенную справку Logisim раздел «Пособие начинающего».

Рис. 3.1. Схема «Логическое И»

1. Разместить на холсте два входных контакта (квадратные), выходной контакт (круглый) и логический элемент AND по образцу рис. 3.1 . Эти элементы вынесены на панель инструментов программы. В свойствах контактов задать их имена (метки) по образцу рис. 3.1 .

2. Использовав инструмент «Рука» из панели инструментов, изменять значения входных контактов и следить, как меняется значение на выходном контакте. Сравнить с таблицей истинности элемента AND.

3. Просмотреть таблицу истинности построенной схемы, использовав пункт главного меню «Проект» – «Анализировать схему» – вкладка «Таблица». Сверить с таблицей из пособия.

3.4.2. Построение одноразрядного полусумматора

Построить одноразрядный полусумматор на основе базовых логических элементов и на основе элементов XOR (рис. 3.2 ), использовав один набор входов для обеих схем. Научиться использовать тоннели.

Рис. 3.2. Варианты схемы одноразрядного полусумматора

1. Построить схему по образцу рис. 3.2 . В свойствах контактов задать соответствующие метки. Входные контакты подключить к тоннелям («Проводка» — «Тоннель»). Направление и метка тоннеля и задаются в его свойствах.

2. Использовав инструмент «Рука» из панели инструментов, изменять значения входных контактов и следить, как меняется значение на выходных контактах. Убедиться, что контакты «s1»/«s2» и «po1»/«po2» показывают равные значения. Сравнить с таблицей истинности одноразрядного полусумматора.

3. Просмотреть таблицу истинности построенной схемы, использовав пункт главного меню «Проект» – «Анализировать схему» – вкладка «Таблица». При появлении предупреждения «Выражение неопределно» нажать кнопку «OK». Сверить с таблицей из пособия.

3.4.3. Построение линии задержки и блоков ввода и вывода

Построить линию задержки на одноразрядных регистрах (рис. 3.3 ). Научиться создавать входной сдвиговый регистр для записи в него начальных значений и выходной сдвиговый регистр для просмотра результата.

Рис. 3.3. Схема линии задержки на 7 тактов

1. Построить схему по образцу рис. 3.3 . Входной и выходной регистры должны иметь разрядность («Биты данных»), равную 1, и длину («Количество ступеней») 16. В свойствах регистров, формирующих линию задержки, указать разрядность («Биты данных»), равную 1. На центральный западный вход входного сдвигового регистра подать однобитовую константу «0». «Бит записи» исходно должен быть равен 0.

2. Использовав инструмент «Рука» из панели инструментов, задать начальные данные для записи во входной регистр.

3. Установить «Бит записи» в «1». Затем однократно нажать кнопку «Такты». Убедиться, что входной регистр проинициализировался. Установить «Бит записи» в «0».

4. Последовательным нажатием кнопки «Такты» передавать биты из входного регистра в линию задержки и далее в выходной регистр. Убедиться, что линия действительно вносит задержку в 7 тактов.

5. Обнулить выходной регистр нажатием соответствующей кнопки.

3.4.4. Построение линии задержки с внесением помехи

Построить линию задержки с внесением помехи (рис. 3.4 ).

Рис. 3.4. Схема линии задержки на 7 тактов с внесением помехи

1. Построить схему по образцу рис. 3.4 . Генератор случайных чисел, играющий роль источника помех, должен иметь разрядность, равную 1. Стоит отметить, что такая схема аналогична двоичному симметричному каналу с вероятностью битовой ошибки 0;5.

2. Использовав инструмент «Рука» из панели инструментов, задать начальные данные для записи во входной регистр.

3. Установить «Бит записи» в «1». Затем однократно нажать кнопку «Такты». Убедиться, что входной регистр проинициализировался. Установить «Бит записи» в «0».

4. Последовательным нажатием кнопки «Такты» передавать биты из входного регистра в линию задержки и далее в выходной регистр (всего 23 такта). Сравнить полученный результат с исходными данными.

5. Обнулить выходной регистр и регистры линии задержки нажатием соответствующей кнопки.

3.5. Порядок защиты практической работы

Защита работы может осуществляться одним из нижеперечисленных способов или их сочетанием на усмотрение преподавателя.

1. Устный ответ по теме работы.

2. Тестирование по теме работы

3. Задача по теме работы.

4. Иные варианты на усмотрение преподавателя.

Logisim — свободный кросплатформенный инструмент моделирования цифровых логических схем. Logisim полностью написан на Java с использованием библиотеки Swing для графического интерфейса пользователя. Соответственно, для запуска Logisim необходимо Java Runtime Environment версии 5 и выше. Среди элементов, которые могут быть включены в схему: элементы ввода и вывода, логические элементы НЕ, И, ИЛИ и т.п. (gates), мультиплексоры, блоки арифметических операций, триггеры, элементы памяти.

Logisim распространяется с поддержкой русского интерфейса и полной документацией на русском языке .

В качестве примеров начинающим кроме официальной документации можно посоветовать библиотеку элементов серии 7400 , любезно предоставленную одним из пользователей Logisim.

Сайт: http://ozark.hendrix.edu/~burch/logisim/index.html

Лицензия: GNU General Public License

Поделиться:

Оставьте свой комментарий!

Logisim стенд для тестирования и проектирования логических схем

Простейший в работе стенд, позволяющий спроектировать структуру ИС и проверить её в работе

Отсуствуют ограничения на число деталей, которые также можно вращать на 360 градусов с шагом 90.

Достаточно мелкий шаг сетки транспаранта позволяет разместить детали более компактно + возможность редактирования обозначений деталей и других мелочей

Год выпуска: 2010

Версия: 2.5.1

Платформа: JRE 1.6

Разработчик: Carl Burch

Системные требования: CPU 1GHz

RAM 128MB

Язык интерфейса: только русский

Таблэтка: Не требуется

Размер архива: 3,75 mb

Скачать с DIOD.UCOZ.RU

Logisim является образовательным инструментом для разработки и моделирования цифровых логических схем. Благодаря простому интерфейсу панели инструментов и моделированию схем по ходу их проектирования, Logisim достаточно прост, чтобы облегчить изучение основных понятий, связанных с логическими схемами. При возможности постройки больших схем из меньших подсхем и рисования пучков проводов одним перетаскиванием мыши, Logisim может быть использован (и используется) для проектирования и моделирования целых процессоров в образовательных целях.

Учащиеся колледжей и университетов по всему миру используют Logisim для различных целей, в том числе:

- Как элемент обзорного курса информатики в общеобразовательных учреждениях

- Как элемент курса организации ЭВМ следующего уровня

- На протяжении всего семестра в курсах архитектуры компьютеров высокого уровня

Руководство «Как стать пользователем Logisim», которое вы сейчас читаете — это официальный обзор возможностей Logisim. Его первая часть представляет собой последовательность разделов, представляющих основные части Logisim. Эти разделы написаны так, что их можно читать «от корки до корки» чтобы узнать обо всех наиболее важных возможностях Logisim.

Пособие начинающего

Библиотеки и атрибуты

Подсхемы

Пучки проводов

Комбинационный анализ

Остальные разделы — разнородная куча справочных материалов и объяснений некоторых тонких моментов в Logisim.

Справка по меню

Компоненты памяти

Запись в журнал

Проверка из командной строки

Настройки приложения

Параметры проекта

Просчёт значений

Библиотеки JAR

О программе

Logisim — инструмент, позволяющий разрабатывать и моделировать цифровые электрические схемы, используя графический интерфейс пользователя. Logisim — свободное программное обеспечение, выпущенное под GNU GPL; может запускаться на Microsoft Windows, Mac OS X, и Linux. Код полностью написан на Java с использованием библиотеки Swing для графического интерфейса пользователя. Основной разработчик, Carl Burch, работает над Logisim с его появления в 2001 году.

Программа чаще всего используется учащимися в курсе изучения информатики для разработки и экспериментов с цифровыми схемами при моделировании. Схемы разрабатываются в Logisim с помощью графического интерфейса, близкого к традиционному для программ для рисования, такой интерфейс встречается во многих других программах для моделирования схем. В отличие от большинства других программ такого назначения, сопоставимых с Logisim по сложности, Logisim позволяет пользователям редактировать схемы в процессе моделирования. Относительная простота интерфейса делает программу удобной для обзорных курсов [1] . Возможности разработки более сложных схем, такие как «подсхемы» и «пучки проводов», имеющиеся в Logisim, доступны в некоторых других графических инструментах с открытым исходным кодом.

Хотя пользователи могут разрабатывать даже полные реализации процессоров, используя Logisim, программа разработана в основном для образовательного использования. Профессионалы обычно разрабатывают такие масштабные схемы, используя языки описания аппаратуры, такие как Verilog или VHDL. Logisim не позволяет работать с аналоговыми компонентами.

Logisim распространяется с поддержкой русского интерфейса и полной документацией на русском языке.

Источник: testirovanie24.ru