Раз уж в прошлой статье я начал рассказывать о принципах оцифровки и воспроизведения звука, то наверное можно и немного рассказать о самом проектировании на ПЛИС. Сегодня я покажу, как реализовать проект «с нуля» — безо всяких makefile и докеров — просто на запущенном Quartus Prime под Windows. Ну а поскольку последним проектом у меня была музыкальная шкатулка , то и продолжу я с той же ноты — сделаю мини-пиано для исполнения кусочка «в лесу родилась ёлочка».

Правда кнопки у меня на плате только 4, много не наиграешь.

Поскольку сегодня формат урока, то начнём с требуемых для его выполнения вещей. Урок ориентирован на Quartus, поэтому нужна плата с ПЛИС от фирмы Altera (выкуплена Intel-ом, так что новые уже идут под Intel-овским брендом). Продвигаемые самим Intel платы стоят как туалет на МКС, поэтому обратимся к китайцам. А китайцы в 2020 году внезапно решили, что на любой уважающей себя плате с ПЛИС обязательно должен быть RS-232 порт ♂️ Вот тольку куда его пихать сегодня. И ладно бы поставили, так они его ставят вместо usb-uart интерфейсов, что совсем огорчает. Зачем они это сделали — непонятно, но если закрыть глаза на него, то вот эта плата выглядит неплохой:

1. ПЛИС (FPGA) Введение

Ну куда в 2020 RS-232 пихать-то?

У неё на борту разъём D-SUB (VGA) для подключения монитора, 7-сегментный индикатор, 8мб оперативки, 1кб eeprom (читай flash) и 2 мегабайта flash-памяти на конфигурационном хранилище (которое и как флешку тоже можно использовать), кнопочки и светодиодики. Главное — в комплекте идёт USB Blaster. Без него плату с компьютером вам не подружить (COM-порт на плате нельзя использовать для прошивки)

Более достойным вариантом я считаю вот эту плату .

Кнопочек маловато, но зато оочень много внешних разъёмов, много оперативки и flash.

Самое главное преимущество — куда как более жирный ПЛИС. на 15к логических элементов вместо 6к. Это значит, что проекты вы на нём сумеете запускать куда как более сложные. В 2 раза больший объём встроенной в ПЛИС оперативки: 504 к бит вместо 273 к бит . Количество ног в 4 раза больше. Так же на плате есть D-SUB, 7-сегментник (но только 3 разряда), тоже кнопочки и тоже светодиодики, 8мб флешки (теперь флешка одна на всё), целых 32 мб оперативки, гигабитный Ethernet! и usb-uart преобразователь. В целом — на порядок лучше предыдущей, хоть в комплекте и не идёт USB Blaster, нужно покупать отдельно .

Стоимостью в 200руб, не велика беда — купить отдельно.

Всё что я указывал — это ценовой диапазон «до 3 000 руб комплект» и с хорошей периферией на борту. Но Aliexpress в помощь, можно найти и вот такой вариант с новеньким Intel (уже Intel) Cyclone 10 на 16к логических элементов и модным HDMI . Или вот такая — пусть и не самая передовая, зато по-настоящему богатая на периферию. В целом — на любой вкус и цвет — такой он алик. Можно даже взять эконом-вариант: CPLD платку . Но нужно понимать, что тут всего 240 логических элементов и ни единого байта встроенной оперативки. Для примера — на всех остальных как минимум 6 000 логических элементов.

Вхождение в ПЛИС за 5 минут

Сам я когда-то купил вот такую платку

Хоть и не всё на ней продумано, но в целом устраивает. Сегодня таких уже не найти.

Кстати, разъём VGA на плате, несмотря на своё устаревание, обладает определёнными преимуществами по сравнению с HDMI. Так как для работы HDMI нужна более высокая частота, то ни о каком Full HD можете и не мечтать — тактировать HDMI понадобилось бы с частотой в пару гигагерц, чего ПЛИС физически не может выполнить. Придётся довольствоваться 640×480. А VGA в той реализации, которая идёт на платах — управляется параллельно. Требуется целых 18 ног от ПЛИС, но заметно более низкая частота — справиться с Full HD уже реально.

Хватит о железках, пора качать Quartus. Если у вас Cyclone IV или новее, то качайте просто самую последнюю Lite версию. Она бесплатна. А вот с более старыми циклонами, придётся качать и более старый квартус. К примеру у меня валяется вот такая платка . Для неё идёт только Quartus 13 и старше.

Даже Quartus 13.1 уже не подходит.

Так же приходится качать 13-й квартус и мне с моим USB Blaster-ом. Возможно китайцы сегодня пихают в них более новые прошивки, но мой на Windows напрочь отказывается дружить с драйверами, идущими в комплекте новых Quartus-ов. Хуже того, сочетание нового драйвера с этим USB Blaster-ом приводит к экранам смерти. Забавненько. Хотя мне от старого Quartus-а нужен только лишь драйвер из комплекта.

Этот старый драйвер дружит и с виндой 10-кой (подписан, сертифицирован, все дела), и с новыми Quartus-ами и с моим USB Blaster-ом. Он идеален.

Но так как Quartus — штука проприетарная, то даже скачка превращается в квест. Обязательно надо зарегится. Без этого никак. Перейти на страницу скачки и выбрать последнюю версию в Lite исполнении. Качать всё не обязательно. Достаточно скачать сам Quartus и пак, содержащий ваш ПЛИС.

Для меня это Cyclone IV device support . Если пака с вашим ПЛИС нет, то смотрите более старые версии Quartus.

Запускаем Quartus Prime. Если у вас Windows или Linux, то это должно вам даться безо всяких усилий. Разные хитрости только на macOS нужны.

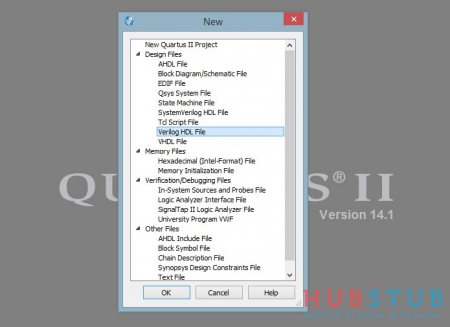

Как только загрузиться главное окно Quartus, нажимаем Ctrl+N . В открывшемся списке выбираете New Quartus Prime Project .

Появится окно, на котором нужно просто нажать Next

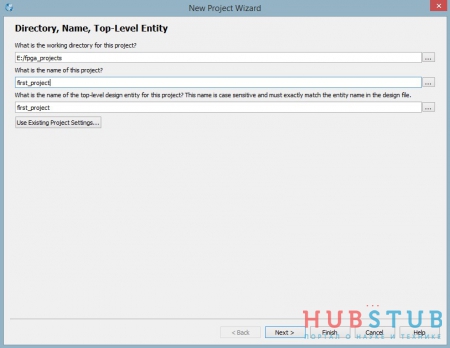

Далее нужно указать, что создавать. В первом поле выбираете папку. И тут внимание — Quartus будет сохранять файлы прямо в эту папку, так что укажите пустую, предназначенную для этого конкретного проекта,

Имя проекта (второе поле) и объекта верхнего уровня (третье) пусть будет top

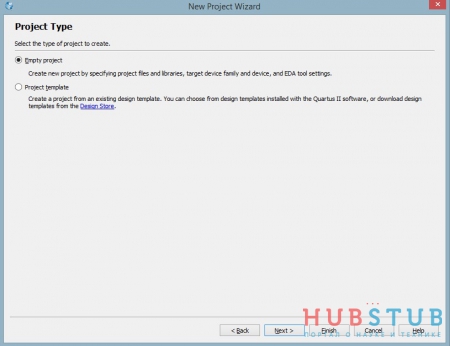

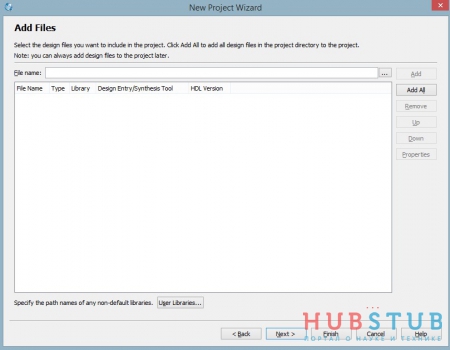

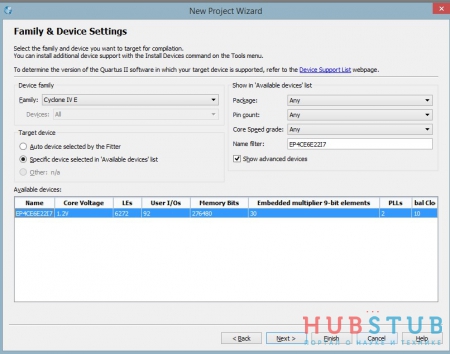

На следующей вкладке оставляете Empty project , и сразу Next , на очередной вам предложат добавить файлы, которых у вас нет, так что снова Next . Так мы и пришли к окну выбора вашего FPGA. На мой взгляд, самый простой способ — это ввести название своего камня в поле

Name filter.

Вводить достаточно до тех пор, покуда не увидите нужное в списке Available devices. Как увидите — выбирайте и жмите сразу Finish , так как ничего интересного больше не будет. Проект готов, нужно добавлять файлы.

Ещё раз нажмите на Ctrl+N . Но теперь выбирайте

Verilog HDL File

И жмите OK .

Открывается новый пустой файл в редакторе, в котором нужно что-то писать.

Вот теперь и начинается тот самый этап, из-за которого я откладывал изучение FPGA несколько лет. Проектирование. И главное, что должен для себя уяснить каждый программист — тут проектируется не программа, а микросхема! При декомпозиции нужно думать, что вы выделяете именно микросхему, а не блок кода. Для программера со стажем это не всегда просто.

Задача данного проекта — выводить на ногу ПЛИС меандр с определённой частотой. Откуда взять — использовать сигнал с присутствующего на платке кварцевого генератора. А генератор присутствует на любой платке ПЛИС. Даже на упомянутой выше CPLD с 240 логическими элементами. Но генератор этот генерирует сигнал высокочастотный: как правило 48 или 50 мгц.

Это несколько выше слухового диапазона. Соответственно частоту меандра надо делить.

Делается это при помощи счётчика, который каждый такт входного сигнала увеличивает своё значение на 1. Как только он достигает своего максимального значения, счётчик сбрасывается а выходная ножка меняет своё состояние на противоположенное. Значит, выбирая различные максимальные значения для счётчика, можно получить различные коэффициенты деления. А следовательно — разную частоту на выходе. Это именно то что надо. Такой счётчик-делитель уже хорошо годиться на выделение в отдельный модуль.

Запомнили и думаем дальше — нам нужно поддержать 4 разные кнопки, и при нажатии на каждую из них должна воспроизводиться своя нота. Сделать это можно 2-мя способами:

1. Держать целых 4 делителя, каждый выводит сигнал определённой частоты. При нажатии кнопки, коммутировать один из делителей с выходом схемы.

Источник: dzen.ru

Первая программа для ПЛИС на Verilog.

В одной из прошлых статей, описывал как прошить ПЛИС уже имеющейся прошивкой, в этой попробуем написать прошивку сами. Начнем с простого — помигаем светодиодом. Для написания программы мы будем использовать язык похожий на С — Verilog.

Для начала создадим проект.

Указываем папку, в которой будет храниться проект, название проекта и название модуля верхнего уровня.

Указываем, что проект будет пустой.

На этом шаге инклудятся файлы, мы его пропускаем.

Выбираем камешек, который будем программировать.

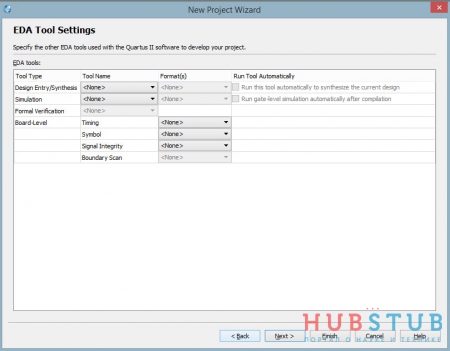

На этом шаге предлагается выбрать средства отладки проекта, мы его пропускаем.

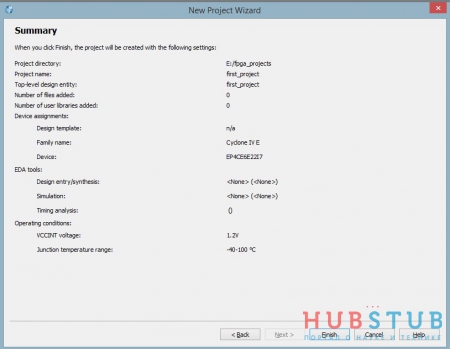

Чек лист для проверки настроек проекта. Если необходимо, любую из настроек можно изменить, вернувшись на несколько шагов назад, используя кнопку Back.

Думаю у многих возник вопрос, что такое модуль верхнего уровня?

Входы и выходы модуля верхнего уровня соединяются непосредственно с выводами микросхемы, также модуль верхнего уровня включает в себя все остальные модули.

Так как проект у нас простой, модуль у нас будет всего один и он же будет модулем верхнего уровня.

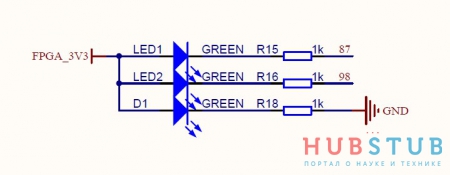

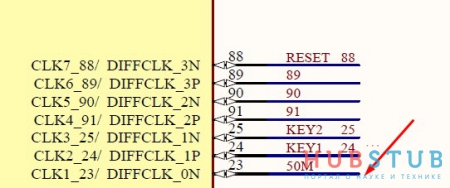

После того как проект создан, откроем схему отладочной платы и посмотрим к какому выводу подключен светодиод и на какой вывод подается тактирование с генератора.

Теперь можно переходить непосредственно к написанию программы. Создаем новый Verilog HDL File, во вкладке File->New.

И пишем следующий код, который изменяет состояние светодиодов два раза в секунду.

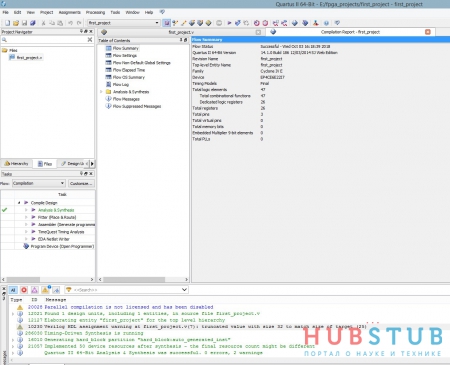

Далее синтезируем проект.

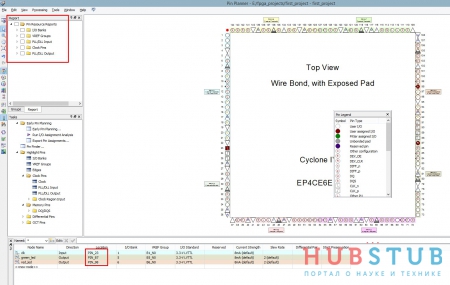

Теперь нужно назначить сигналам реальные выводы микросхемы во вкладке Pin Planner.

В столбце location указал какие выводы каким сигналам будут соответствовать. Хотелось бы отметить, что нельзя назначить сигналу любой вывод микросхемы потому, что сигналы разделены на 5 групп и каждая из них имеет свое назначение, на скриншоте они выделены красным квадратом. Первая группа — привычные выводы входа/выхода, на вторую группу заводятся опорные напряжения для каждого банка отдельно, третья и пятая — это вход и выход PLL, а на выводы четвертой группы заводится тактовый сигнал.

Теперь необходимо запустить компиляцию.

В результате компиляции генерируется файл .sof, который можно зашить в ПЛИС.

Источник: hubstub.ru

FPGA. Просто о сложном — Философия написания конфигураций для ПЛИС

В предыдущей статье цикла «FPGA. Просто о сложном» было рассмотрено внутреннее устройство FPGA, в этой статье пойдет речь о том, как пишется конфигурация для этих БИС. Дело в том, что все статьи для новичков, которые мне попадались, были типа «помигать светодиодиком» либо на ALTERA, либо на Xilinx и не раскрывали философии параллельности вычислений.

Да, Вы все правильно поняли, в ПЛИС все вычисления выполняются параллельно В этой статье я постараюсь рассказать о том, как пишется конфигурация для ПЛИС без привязки к какому либо производителю. Все примеры будут представлены на VHDL.

Бытует мнение, что Verilog более понятен, но если честно, это только «дело религии» на каком языке писать, в любом случае, все сказанное будет справедливо и для Verilog. После прочтения этой статьи, Вы будете иметь представление как писать под ПЛИС любой фирмы в любом IDE на любом языке.

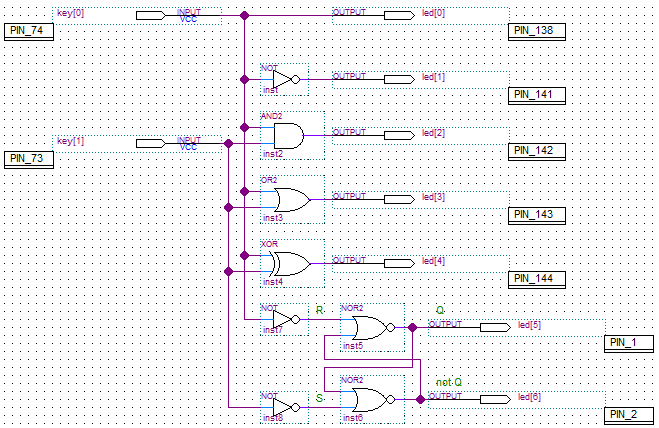

Для начала давайте разберемся зачем нужно делать конфигурацию на VHDL или Verilog, ведь в интернете полно примеров с редакторами, в которых нужно просто соединять элементы «И», «И-НЕ», и т.д., чтобы получить требуемую схему. Например как на рисунке ниже:  Может показаться, что это удобно, ведь все наглядно и привычно, но только как будет выглядеть схема если Вам вдруг понадобится добавить в проект хотя бы одно fifo?

Может показаться, что это удобно, ведь все наглядно и привычно, но только как будет выглядеть схема если Вам вдруг понадобится добавить в проект хотя бы одно fifo?

А если в проекте нужно реализовать БПФ (быстрое преобразование Фурье)? Такая схема разрастется до эпических масштабов так что учите язык, не издевайтесь над собой. На предприятиях специализирующихся на разработке под ПЛИС подобная реализация конфигураций уже лет 30 как не делается, все пишется с помощью VHDL или Verilog, потому что это быстрее и понятнее.

Раз мы выяснили, что единственный путь для создания крупных проектов это языки VHDL или Verilog, то приступим к рассмотрению приемов программирования, но перед этим учтем несколько нюансов: 1) Все проекты состоят из модулей написанных на языке описания, которые обладают портами для связи с другими модулями. 2) Любые операции могут быть синхронными (производятся только по сигналу тактирования), либо асинхронными (не зависят от сигнала тактирования и производятся в любой момент времени).

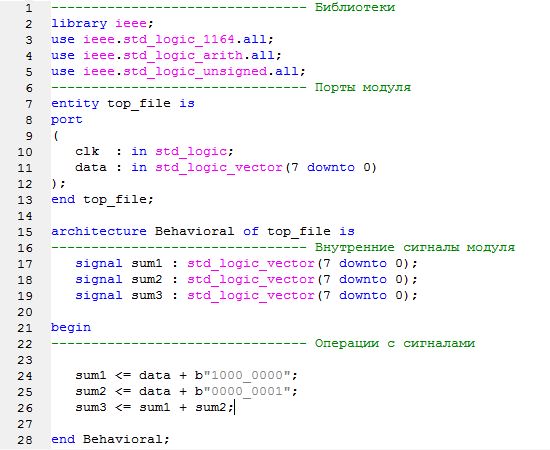

Ниже на картинке представлен пример асинхронных вычислений, давайте его разберем: на вход clk подается тактовый сигнал. Тактовый сигнал нужен для синхронизации других сигналов по времени и его источником обычно выступает кварцевый генератор, конкретно в этом примере он нужен только для наглядности и нигде не используется. На входную 8-битную шину data подаются 8-битные слова x»01″, x»02″, x»03″, x»04″, источником данных на этой шине может служить любой другой модуль в этой же ПЛИС или же, если привязать эту шину к реальным портам, любой другой источник из внешнего мира . Сигналы sum1 и sum2 по-сути являются 8-битными регистрами, куда мы помещаем значение суммы между приходящим по шине data словом и некоторым прибавляемым значением. Сигнал sum3 является результатом суммирования sum1 и sum2. Вычисления sum1, sum2, и sum3 выполняются асинхронно, это значит, что вычисления происходят мгновенно с изменением сигнала data и никак не синхронизируются по тактовому сигналу.  (Примечание: b»1000_000″ это бинарная запись шестнадцатиричного числа x»80″, а b»0000_0001 это x»01″)

(Примечание: b»1000_000″ это бинарная запись шестнадцатиричного числа x»80″, а b»0000_0001 это x»01″)

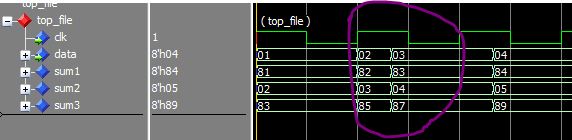

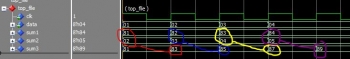

Теперь давайте посмотрим на осциллограмму ниже. Вы можете убедиться, что операции вычисления sum1 и sum2 и sum3 выполнялись параллельно и асинхронно, т.е. над одним и тем же значением сигнала data одновременно проводились две разные операции sum1 и sum2, и в этот же момент времени производилась операция суммирования между sum1 и sum2.

Также на осциллограмме ниже видно, что за один такт пришло два слова (асинхронность обведена фиолетовым), но это никак не повлияло ни на время вычислений, ни на их результат.  Теперь слегка изменим программу: добавим синхронизацию вычисления sum3 по фронту тактового сигнала clk и получим пример синхронных вычислений.

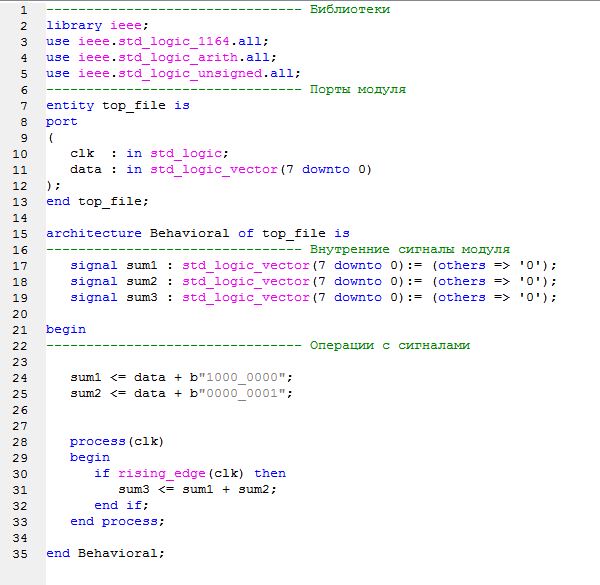

Теперь слегка изменим программу: добавим синхронизацию вычисления sum3 по фронту тактового сигнала clk и получим пример синхронных вычислений.

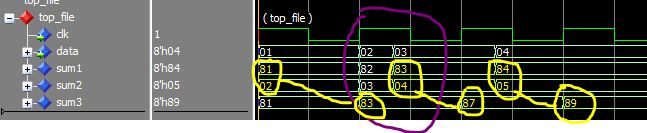

Если раньше значение sum3 вычислялось одновременно с sum1 и sum2, то теперь, как видно из осциллограммы ниже, значение sum3 вычисляется только с наступлением фронта тактового сигнала, т.е. на следующий такт. Такие задержки в такт нужно учитывать при написании синхронных процессов.

Если раньше значение sum3 вычислялось одновременно с sum1 и sum2, то теперь, как видно из осциллограммы ниже, значение sum3 вычисляется только с наступлением фронта тактового сигнала, т.е. на следующий такт. Такие задержки в такт нужно учитывать при написании синхронных процессов.

Кроме того, на осциллограмме видно, что в момент, когда за один такт на шину data пришло два слова, вычисления произошли лишь над вторым словом, так-как оно было последним установившимся значением перед фронтом тактового сигнала.  На осциллограмме ниже проиллюстрировано, как происходят те же вычисления если синхронизировать источник, посылающий на шину data данные, с тактовым сигналом (с каждым тактом приходит только одно слово): мы провели операции суммирования со всеми входными данными ничего не потеряв.

На осциллограмме ниже проиллюстрировано, как происходят те же вычисления если синхронизировать источник, посылающий на шину data данные, с тактовым сигналом (с каждым тактом приходит только одно слово): мы провели операции суммирования со всеми входными данными ничего не потеряв.

Логично спросить, мол, зачем вообще нужна синхронизация, если все можно делать асинхронно и выигрывать в скорости? Ответ прост: чтобы иметь возможность проводить определенные вычисления в определенный момент времени. Например стоит задача принять пакет из 100 8-битных слов и в 99 слово записать какое-то свое значение, чтобы отправить его дальше.

Логично спросить, мол, зачем вообще нужна синхронизация, если все можно делать асинхронно и выигрывать в скорости? Ответ прост: чтобы иметь возможность проводить определенные вычисления в определенный момент времени. Например стоит задача принять пакет из 100 8-битных слов и в 99 слово записать какое-то свое значение, чтобы отправить его дальше.

Зная, что за один такт нам может придти только одно слово, не трудно завести счетчик и посчитать до 99. Подводя итоги к этой статье могу сказать, что никто не запрещает Вам писать как синхронные процессы так и асинхронные, комбинировать их, все зависит от ситуации: если требуется привязка ко времени (всякие разные протоколы, интерфейсы, счетчики/таймеры и т.д), то делайте синхронизацию, если нужно словить изменение сигнала в любой неопределенный момент времени то делайте процесс асинхронным. Автор старался излагать максимально доступно, спасибо что дочитали до конца.

Теги:

sboldenko

sboldenko  Опубликована: 12.02.2017

Опубликована: 12.02.2017  0

0  2

2

Источник: cxem.net