Любой IBM PC совместимый компьютер построен по принципу описанному ещё Джорджем фон Нейманом в 1945м году, его основные составляющие – блок управления, арифметико-логическое устройство, память и устройство ввода-вывода. В компьютере реализован принцип хранимой программы, т.е. данные и программа хранятся в одной и той же памяти. ЦП выбирает и исполняет команды из памяти последовательно, адрес следующей команды задаётся счётчиком адреса, такой принцип называется последовательной передачей управления. Подобная архитектура является не единственно приемлемой, есть ещё потоковые компьютеры и разрабатываются новые типы вычислительных машин.

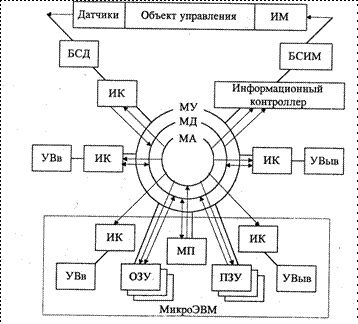

На рис. 1 приведена схема логической структуры микро¬процессорной системы. МикроЭВМ — это совокупность микропроцессора (МП), ОЗУ и ПЗУ вместе с устройствами ввода-вывода (УВВ), предназначенными для работы с оператором или с другой электронной системой. В МП систему входит также аппаратурный блок — информационный контроллер ИК, приводящий все связи и сигналы УВВ разных типов к стан¬дартному виду. ИК имеет стандартный интерфейс со стороны подключения к информационной магистрали, состоящей из ма¬гистралей адресов, данных и управления (МА, МД, МУ), и нестандартный интерфейс со стороны УВВ.

8 урок. Принципы Фон-Неймана

МикроЭВМ становится центральной частью электронной системы контроля и управления, когда она вводится в контур управления некоторого объекта (процесса) ОУ. Для сопряжения с микроЭВМ ОУ оснащается датчиками состояния (Д) и исполнительными механизмами (ИМ). Для согласования интерфейсов Д и ИМ подключаются через блоки сопряжения (БС).

Рассмотренная структура отражает магистрально-модульный принцип организации МПС. Отдельные блоки являются функци¬онально законченными модулями со своими встроенными схемами управления, выполненными в виде одного или нескольких кристаллов БИС, заключенных в корпуса с соответствующим числом выводов. Межмодульные связи и обмен информацией меж¬ду модулями осуществляются посредством магистралей — коллективных шин.

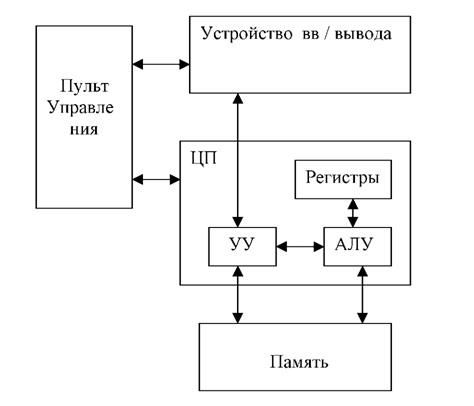

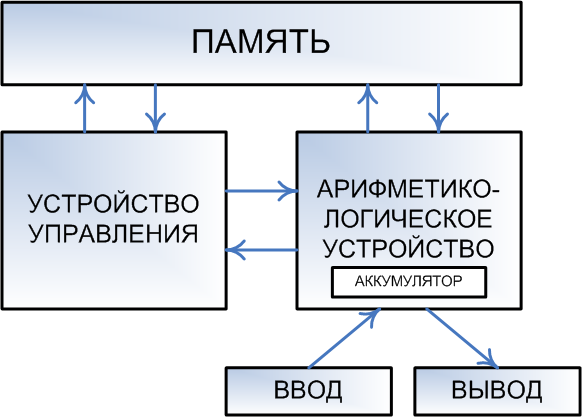

Структура ВМ классической фон Неймановской архитектуры

Она состоит из 4 основных узлов: центрального процессора (ЦП), памяти, устройств ввода / вывода (УВВ) и пульта управления. ЦП состоит из арифметико—логического устройства (АЛУ), устройства управления (УУ) и регистров (регистрового файла). Внешние устройства (УВВ) служат для ввода в память программы и исходных данных и вывода результатов. Пульт управления служит для первоначального запуска машины, контроля хода вычисления, остановки вычислений вручную и др.

Арифметические и логические операции выполняются в АЛУ над целыми, вещественными числами и логическими элементами, представленными в двоичной системе счисления. Для отрицательных значений используется обратный или дополнительный код. Последний используется чаще, т. к. позволяет свести операцию вычитания к операции сложения. Дополнительный код получается при инверсии значащих разрядов числа и добавления в младший разряд единицы.

Принципы фон Неймана

В состав обычного фон Неймановского компьютера входит один ЦП, основная задача которого — выбирать из памяти и выполнять команды. Порядок выборки команд определяется счётчиком адреса команд (СЧАК), содержимое которого инкрементируется после выборки очередной команды. Изменение естественного порядка выборки и выполнения команд производится командами переходов (передач управления), засылающих целевой адрес в СЧАК.

Выбранная команда дешифрируется УУ и интерпретируется им в последовательность импульсов и потенциалов (микроопераций), управляющих соответствующими операциями функциональных узлов ЭВМ.

ЦП имеет набор регистров или сверхоперативную память, предназначенную для временного хранения промежуточных результатов и данных, нужных для выполнения команд. Регистры делятся на два класса -регистры общего назначения (РОН) и специальные. РОНы доступны программисту и их функциональность может меняться программно. Их количество широко варьруется в разных процессорах и ограничивается технологическими и экономическими соображениями. Операционные регистры, к которым относятся регистр команд, разные буферные регистры недоступны программисту.

В архитектуре фон Неймана применяется однородная память микропроцессора. В эту память могут записываться различные программы. При этом специальная программа-загрузчик работает с ними как с данными. Затем управление может быть передано этим программам и они уже начинают выполнять свой алгоритм. При подобном подходе к управлению микропроцессором удается достигнуть максимальной гибкости микропроцессорной системы.

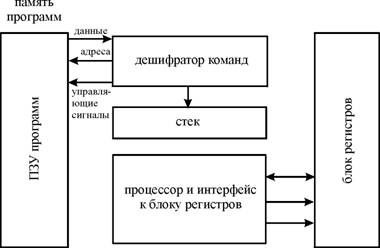

Структура Гарвардской архитектуры

В качестве недостатка архитектуры фон Неймана можно назвать возможность непреднамеренного нарушения работоспособности системы (программные ошибки) и преднамеренное уничтожение ее работы (вирусные атаки). В Гарвардской архитектуре принципиально различаются два вида памяти микропроцессора:

• Память программ (для хранения инструкций микропроцессора)

• Память данных (для временного хранения и обработки переменных)

В гарвардской архитектуре принципиально невозможно осуществить операцию записи в память программ, что исключает возможность случайного разрушения управляющей программы в случае ошибки программы при работе с данными или атаки третьих лиц. Кроме того, для работы с памятью программ и с памятью данных организуются отдельные шины обмена данными (системные шины), как это показано на рисунке 3.

Эти особенности определили области применения гарвардской архитектуры. Гарвардская архитектура применяется в микроконтролерах и в сигнальных процессорах, где требуется обеспечить высокую надёжность работы аппаратуры. В сигнальных процессорах Гарвардская архитектура дополняется применением трехшинного операционного блока микропроцессора. Трехшинная архитектура операционного блока позволяет совместить операции считывания двух операндов с записью результата выполнения команды в оперативную память микропроцессора. Это значительно увеличивает производительность сигнального микропроцессора без увеличения его тактовой частоты.

В Гарвардской архитектуре характеристики устройств памяти программ и памяти данных не всегда выполняются одинаковыми. В памяти данных и команд могут различаться разрядность шины данных и распределение адресов памяти. Часто адресные пространства памяти программ и памяти данных выполняют различными. Это приводит к различию разрядности шины адреса для этих видов памяти.

В микроконтроллерах память программ обычно реализуется в виде постоянного запоминающего устройства, а память данных — в виде ОЗУ. В сигнальных процессорах память программ вынуждены выполнять в виде ОЗУ. Это связано с более высоким быстродействием оперативного запоминающего устройства, однако при этом в процессе работы осуществляется защита от записи в эту область памяти.

Применение двух системных шин для обращения к памяти программ и памяти данных в гарвадской архитектуре имеет два недостатка — высокую стоимость и большое количество внешних выводов микропроцессора. При использованиии двух шин для передачи команд и данных, микропроцессор должен иметь почти вдвое больше выводов, так как шина адреса и шина данных составляют основную часть выводов микропроцессора. Для уменьшения количества выводов кристалла микропроцессора фирмы-производители микросхем объединили шины данных и шины адреса для внешней памяти данных и программ, оставив только различные сигналы управления (WR, RD, IRQ) а внутри микропроцессора сохранили классическую гарвардскую архитектуру. Такое решение получило название модифицированная гарвардская архитектура.

Модифицированная гарвардская структура применяется в современных микросхемах сигнальных процессоров. Ещё дальше по пути уменьшения стоимости кристалла за счет уменьшения площади, занимаемой системными шинами пошли производители однокристалльных ЭВМ — микроконтроллеров. В этих микросхемах применяется одна системная шина для передачи команд и данных (модифицированная гарвардская архитектура) и внутри кристалла.

В сигнальных процессорах для реализации таких алгоритмах как быстрое преобразование Фурье и цифровая фильтрация часто требуется еще большее количество внутренних шин. Обычно применяются две шины для чтения данных, одна шина для записи данных и одна шина для чтения инструкций. Подобная структура микропроцессора получила название расширенной гарвардской архитектуры. Этот подход практикуют производители сигнальных процессоров — фирмы Analog Devices (семейства сигнальных процессоров BlackFin и Tiger Shark), Texas Instrunents (семейства сигнальных процессоров C5000™ DSPs и C6000™ DSPs), Freescale (семейства сигнальных процессоров MSC8251 и DSP56K).

Источник: www.drive2.ru

Фон-неймановская и гарвардская архитектуры

Архитектура микропроцессора. Основные понятия

Под архитектурой МП понимают принцип его внутренней организации: общую структуру, логическую структуру отдельных устройств, совокупность команд и принципы взаимодействия аппаратной части и программы обработки информации.

Иначе: архитектура – математическая модель МП, образованная программно- доступными элементами МП. Архитектура МП отражает возможности прикладного использования МП и содержит описание программной модели МП. Под программной моделью микропроцессора понимается совокупность программно-доступных регистров, объединенных в систему укрупненными связями и дополнительными элементами, обеспечивающими функциональную законченность модели.

Полностью понятие архитектура МП включает:

— структурную схему МП,

— программную модель МП,

— описание организации памяти,

— описание организации процедур ввода/вывода.

Различают два основных типа архитектуры МП – фон Неймановскую (принстонскую) и гарвардскую.

| Фоннеймановская архитектура | Гарвардская архитектура |

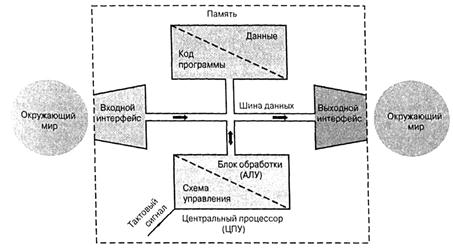

Фон Неймановская (принстонская) архитектура (предложена Джо фон Нейманом в 1945 г.) предполагает, что программа и данные находятся в общей памяти, доступ к которой производится по одной шине данных и команд. Основным достижением группы инженеров, работавших с Джоном фон Нейманом, было осознание того факта, что программа может храниться в памяти вместе с данными.

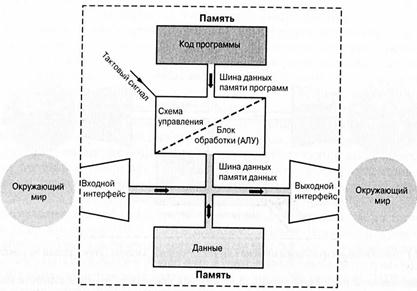

Основным преимуществом такого подхода является его гибкость, так как для изменения программы достаточно просто загрузить новый код в соответствующую область памяти. По существу, фон-неймановская архитектура, показанная на рис., состоит из центрального процессора (ЦПУ), памяти и общей шины (магистрали), по которой в обоих направлениях пересылаются данные. ЦПУ также должен взаимодействовать и с окружающим миром. При этом данные к/от соответствующих интерфейсных портов передаются по одной общей шине данных.

Огромным преимуществом фон-неймановской архитектуры является ее простота, поэтому данная концепция легла в основу большинства компьютеров общего назначения. Однако использование общей шины означает, что в любой момент времени может выполняться только одна операция. Соответственно, пересылка данных между ЦПУ и памятью данных не может осуществляться одновременно с выборкой команды . Эта особенность называется фон-неймановским узким местом.

|

Рис. – Элементарная фон-неймановская машина (шина адреса не показана) |

Гарвардская архитектура (реализована в 1944 г. в ЭВМ Гарвардского университета) соответствует структуре с разделенными устройствами памяти команд и данных и отдельными шинами команд и данных.

В первое послевоенное десятилетие в Гарвардском университете было создано несколько компьютеров семейства «Марк», в которых память программ была полностью отделена от памяти данных (программа считывалась с бумажной перфоленты). Такая концепция была более эффективной, чем фон-неймановская (принстонская) архитектура, поскольку код программы мог считываться из памяти программ одновременно с обменом между ЦПУ и памятью данных или с операциями ввода/вывода. Однако такие машины были намного сложнее и дороже в изготовлении. А с учетом уровня технического развития 40 — 50-х годов, высоких экономических затрат, они не получили широкого распространения. Однако с развитием больших интегральных схем и технологии гарвардская архитектура снова оказалась в центре внимания.

Рис. – Элементарная гарвардская машина (шина адреса не показана) Рис. – Элементарная гарвардская машина (шина адреса не показана) |

На Рис. показаны две физически разделенные шины, используемые для передачи информации между ЦПУ и неперекрывающимися областями памяти. Каждая память имеет собственную шину адреса, поэтому адрес ячейки памяти программ никоим образом не связан с адресом ячейки памяти данных. В таком случае говорят, что обе области памяти находятся в различных адресных пространствах. Память данных иногда называют файловой памятью, в этом случае n -я ячейка обозначается как файл n. |

| Фоннеймановская архитектура более экономно расходует аппаратные ресурсы, а гарвардская позволяет реализовать большее быстродействие. |

Понравилась статья? Добавь ее в закладку (CTRL+D) и не забудь поделиться с друзьями:

Источник: studopedia.ru

1. Архитектура эвм. Архитектура Фон-Неймана.

Архитектура фон Неймана — широко известный принцип совместного хранения программ и данных в памяти компьютера. Вычислительные системы такого рода часто обозначают термином «машина фон Неймана», однако соответствие этих понятий не всегда однозначно. В общем случае, когда говорят об архитектуре фон Неймана, подразумевают физическое отделение процессорного модуля от устройств хранения программ и данных.

Принципы фон Неймана

Принцип двоичного кодирования

Согласно этому принципу, вся информация, поступающая в ЭВМ, кодируется с помощью двоичных сигналов (двоичных цифр, битов) и разделяется на единицы, называемые словами.

Принцип однородности памяти

Программы и данные хранятся в одной и той же памяти. Поэтому ЭВМ не различает, что хранится в данной ячейке памяти — число, текст или команда. Над командами можно выполнять такие же действия, как и над данными.

Принцип адресуемости памяти

Структурно основная память состоит из пронумерованных ячеек; процессору в произвольный момент времени доступна любая ячейка. Отсюда следует возможность давать имена областям памяти, так, чтобы к хранящимся в них значениям можно было бы впоследствии обращаться или менять их в процессе выполнения программы с использованием присвоенных имен.

Принцип последовательного программного управления

Предполагает, что программа состоит из набора команд, которые выполняются процессором автоматически друг за другом в определенной последовательности.

Принцип жесткости архитектуры

Неизменяемость в процессе работы топологии, архитектуры, списка команд.

Компьютеры, построенные на принципах фон Неймана

- Манчестерский Марк I (прототип — Манчестерская малая экспериментальная машина). Манчестерский университет, Великобритания, 21 июня 1948 года;

- EDSAC. Кембриджский университет, Великобритания, 6 мая 1949 года;

- BINAC. США, апрель или август 1949 года;

- CSIR Mk 1. Австралия, ноябрь 1949 года;

- SEAC. США, 9 мая 1950 года

2. Архитектура эвм. Гарвардская архитектура.

Гарвардская архитектура — архитектура ЭВМ, отличительными признаками которой являются: 1. Хранилище инструкций и хранилище данных представляют собой разные физические устройства. 2. Канал инструкций и канал данных также физически разделены.

Архитектура была разработана Говардом Эйкеном в конце 1930-х годов в Гарвардском университете.

Классическая гарвардская архитектура

Типичные операции (сложение и умножение) требуют от любого вычислительного устройства нескольких действий:

- выборку двух операндов,

- выбор инструкции и её выполнение,

- и, наконец, сохранение результата.

Идея, реализованная Эйкеном, заключалась в физическом разделении линий передачи команд и данных. В первом компьютере Эйкена «Марк I» для хранения инструкций использовалась перфорированная лента, а для работы с данными — электромеханические регистры. Это позволяло одновременно пересылать и обрабатывать команды и данные, благодаря чему значительно повышалось общее быстродействие компьютера.

В Гарвардской архитектуре характеристики устройств памяти для инструкций и памяти для данных не требуется иметь общими. В частности, ширина слова, тайминги, технология реализации и структура адресов памяти могут различаться. В некоторых системах инструкции могут хранится в памяти только для чтения, в то время как, для сохранения данных обычно требуется память с возможностью чтения и записи. В некоторых системах требуется значительно больше памяти для инструкций, чем памяти для данных (поскольку данные обычно могут подгружатся с внешней или более медленной памяти). Такая потребность увеличивает битность (ширину) шины адреса памяти инструкций по сравнению с шиной адреса памяти данных.

Модифицированная гарвардская архитектура

Соответствующая схема реализации доступа к памяти имеет один очевидный недостаток — высокую стоимость. При разделении каналов передачи команд и данных на кристалле процессора последний должен иметь почти вдвое больше выводов, так как шина адреса и шина данных составляют основную часть выводов микропроцессора. Способом решения этой проблемы стала идея использовать общие шину данных и шину адреса для всех внешних данных, а внутри процессора использовать шину данных, шину команд и две шины адреса. Такую концепцию стали называть модифицированной Гарвардской архитектурой.

Такой подход применяется в современных сигнальных процессорах. Ещё дальше по пути уменьшения стоимости пошли при создании однокристалльных ЭВМ — микроконтроллеров. В них одна шина команд и данных применяется и внутри кристалла.

Разделение шин в модифицированной Гарвардской структуре осуществляется при помощи раздельных управляющих сигналов: чтения, записи или выбора области памяти.

Расширенная гарвардская архитектура

Часто требуется выбрать три составляющие : два операнда и инструкцию (в алгоритмах цифровой обработки сигналов это наиболее распространенная задача в БПФ и КИХ, БИХ фильтрах). Для этого существует кэш-память. В ней может храниться инструкция — следовательно, обе шины остаются свободными и появляется возможность передать два операнда одновременно. Использование кэш-памяти вместе с разделёнными шинами получило название «Super Harvard Architecture» («SHARC») — расширенная Гарвардская архитектура.

Примером могут служить процессоры «Analog Devices»: ADSP-21xx — модифицированная Гарвардская Архитектура, ADSP-21xxx(SHARC) — расширенная Гарвардская Архитектура.

Источник: studfile.net