Jtag что это за программа

Описание eMMC

Сейчас и в дальнейшем, при описании работы с EMMC мы будем отталкиваться от работы в программе eMMC tool, которую также называют Easy Jtag Plus.

Модуль eMMC_tool предствляет собой развитие программы EasyJtag Classic в области работы с eMMC. Данный модуль объединяет собой несколько программ типа Direct Odin и Direct Qualcomm, которые изначально были написаны для попыток записи прошивок напрямую в eMMC и общей работы c eMMC.

Основная кнопка программы это Detect EMMC, для проверки подключения и определения, «живая» ли микросхема вообще, т.е. реагирует она на внешние комманды или нет. По данной команде из микросхемы вычитываются основные данные: CID, CSD, размеры разделов, основные биты конфигурации, хранящиеся в Extended CSD (ExtCSD).

CID содержит информацию о производителе микросхемы, название микросхемы, месяц год производства и серийный номер.

ExtCSD представляет собой блок регистров (512 байт), в которых хранится конфигурация микросхемы.

JTAG Граничное тестирование

Сама микросхема eMMC представляет собой память с контроллером (интерфейсом), и с точки зрения устройства содержит в себе

1) 4 основных раздела ( ROM1, ROM2, ROM3, RPMB ),

2) до 4 разделов GP ( GP1-GP4 ),

3) регистры конфигурации Extended CSD (ExtCSD)

ROM1 — Main User Datа , иногда называется Userdata;

ROM2 — Boot Partition 1 (Boot1);

ROM3 — Boot Partition 2 (Boot2);

ROM4 — так иногда называют раздел GP1 .

Раздел ROM1 является основным разделов в который пишутся данные (прошивка), и содержит в себе все разделы,

сформированные с помощью таблицы разделов.

ROM2,3 (Boot1,2) являются разделами в котором хранится загрузчик, отправляемый в процессор

(например, MTK (Mediatek), Exynox (Samsung)), или откуда процессор сам его берет (Intel, HiSilicon)

RPMB — защищенный от прямого чтения/записи раздел, предназначенный для хранения данных, к которым должен быть затруднен доступ извне. Данные в этом разделе доступны только через процессор устройства, который получает в него доступ использующий ключ, содержащий с себе SN процессора и еще какие-то данные. Для работы с этим разделом в процессорах содержится специальный блок, который шифрует данные и работает с этим разделом, предварительно согласовав ключи с микросхемой, в которой их еще нет. Достоверных данных о возможности работать с этот разделом минуя процессор, неизвестно.

Разделы GP1-GP4 , это разделы, которые создаются за счет начала раздела ROM1 и физически располагаются на его месте, уменьшая собой размер ROM1. На данный момент такие разделы, а точнее один (GP1) создаются в устройствах, собранных на процессорах Intel (но не на всех, в частности на платформе CloverView).

Размеры ROM2/3/RPMB можно изменить только на EMMC Samsung до ревизии Extended CSD v1.8 (MMC v 5.1), в остальных случаях их размер остается таким, каким его задали на заводе. В большинстве случаев размер не имеет значения, потому как обычно загрузчики редко превышают размер 512KB. Но есть аппараты, которые используют RPMB и отказываются работать с микросхемами, которые предназначены для аппаратов с процессорами Tegra (Nvidia), в которых обычно конфигурируется размер RPMB равным нулю

Интерфейс JTAG

Также для процессоров MTK со scatter файлами первых версий (например, для процессоров MT6589), сумма размеров ROM2/3/RPMB не может быть больше начала раздела MBR, который должен быть записан по адресу указанному в scatter, который для MT6589 процессора равен 0x600000 (6MB).

Поэтому eMMC с размерами ROM2/3/RPMB 2/2/2MB или 2/2/0,5MB будет работать с MT6589, а с размерами ROM2/3/RPMB 4/4/4 уже не будет.

Раздел(ы) GP1 создаются на всех типах eMMC, поддерживающих General Partition Configuring, однократно. При этом наблюдались проблемы с созданием разделов GP1-GP4 на микросхемах Toshiba.

Лог детакта eMMC, базовая информация о eMMC.

В настройках eMMC_Tool есть галочка «Shot info about eMMC in log». Данная настройка позволяет выводить только основную информацию в логе детекта eMMC.

Первые строки позволяют понять, есть ли физический контакт по линии CMD, которая служит основной линией передачи команд в eMMC.

Т.к. eMMC имеет 2 напряжения, VCC (собственно питание микросхемы) и VCCQ (или VIO — напряжение линии ввода-вывода), то интерфейс обмена eMMC работает с логическими уровнями VCCQ. Поэтому важно, чтобы в интерфейсе программы было выставлено напряжение VIO равное напряжению на адаптере eMMC, обычно это 1,8v.

Тем не менее, при нестабильности коннекта можно увеличить VIO в программе, это позволит за счет перетока тока из бокса в интерфейс eMMC улучшить коннект с проблемным подключением. Настоятельно не рекомендуется повышать больше чем на 1 шаг или ставить ниже реального VCCQ.

Теперь становятся понятным следующие 2 строки:

CMD Pullup Level: — уровень напряжение линии CMD, которое выдает бокс;

CMD Active Level: — уровень сигнала, которое отдает микросхема.

Если CMD Active Level сильно занижено ( 300-500mV ), это значит обычно отсутствие контакта по линии CMD или отсутствие PullUp резисторов между линией CMD и VCCQ в интерфейсе подключения eMMC. Если занижен CMD PullUp Level, это значит, что линия CMD закорочена на землю.

Дальше в логе выводится CID, CSD, потом идет расшифровка CID — из него выделяется для наглядности Brand eMMC (Samsung), eMMC NAME (M8G2FB), Serial Number (S/N: D31CE4AC), версию прошивки firmware eMMC (rev.00).

Дальше выводятся размеры ROM1, ROM2, ROM3, RPMB. Т.к. размеры ROM2/3 всегда одинаковы, они выводятся одной строкой.

Одной из важных строк является версия ExtCSD, которая показывает поколение eMMС, а точнее — стандарт команд, который она поддерживает. При замены eMMC в аппарате нужно знать, что в большинстве случаев более новую eMMC нельзя заменить более старой.

Для того, чтобы в процессе работы с eMMC были видны основные ее параметры, они дублируются над логом одной строкой или по нажатию на кнопку под ней в расширенном виде с расшифровкой.

В первой строке выводится краткая информация: EMMC Brand, NAME, информация о разделе загрузки (boot from, являющегося расшифровкой регистра 179 ExtCSD, кол-во линий data по которым передается boot, записанное в регистре 177 ExtCSD (bus config).

В расширенном варианте также отображаются цифровые значения регистров 179/177 ExtCSD, значение регистра 162 ExtCSD с расшифровкой.

Кроме этого выводится значение регистра конфигурации [PARTITION_SETTING_COMPLETED], 0x01 в котором означает, что раздел ROM1 окончательно сконфигурирован, и создание в нем или изменение разделов GP1-GP4 невозможно.

Последняя строка — значения регистров ExtCSD, которые показывают выставлен ли режим RO (ReadOnly — только чтение) в eMMC.

Temporary Write Protection это временный флаг, который можно легко снять, он выставляется во время загрузки Boot в аппаратах Lumia (и может еще где-то).

Permanent Write Protection выставляется eMMC при ее длительном износе, и говорит обычно о том, что срок службы eMMC пришел к концу.

В расширенном варианте лога выводится еще строка информация по регистру ExtCSD [PARTITIONING_SUPPORT], который отображает возможности eMMC к созданию дополнительных разделов GP1-GP4, битовый регистр, может иметь значения 0x00, 0x01, 0x03, 0x07. Из них 0x00 означает, что микросхема не поддерживает создание GP1-GP4, остальные значения связаны с вариантами конфигурирования GP1-GP4, чем больше значение тем больше опций при создании этих разделов поддерживает eMMC.

Частично или полностью неисправные eMMC.

Признаки плохого контакта eMMC в сокете или же полной неисправности eMMC являются строки:

Can’t init device. Reason: CMD Timeout Error

Can’t init device. Reason: OCR Ready Timeout Error [Check VCC or eMMC DEAD]

Can’t init device. Reason: CARD is Password Locked

У полуживых микросхем в CID выдается информация, которая говорит о том, что микросхема находится в boot-режиме.

примеры:

Sandisk:

EMMC NAME: SDM 032 , S/N: FFFFFFFF , rev. 90

EMMC ROM 1 (Main User Data) Capacity: 30 MB (000001E9C000)

Hynix:

EMMC NAME: M MOR , S/N: 00000000 , rev. 00

EMMC ROM 1 (Main User Data) Capacity: 128 MB (000008000000)

FORESEE

EMMC NAME: , S/N: FFFFFFFF , rev. FF

EMMC NAME (HEX ): 000000000000

Samsung

EMMC NAME: 000000 , S/N: 20110726 , rev. 56

EMMC NAME (HEX): 303030303030

Признаком boot-режима eMMC Samsung является eMMC NAME 000000, и rev.0x56. Так же выглядит запуск eMMC Samsung используя TP (test-point). В eMMC Samsung до MMC rev 5.0 (и в некоторых rev 5.0), чаще всего можно восстановить прошивку eMMC, но это не всегда гарантирует, что она после этого долго проработает (зависит от причины, по которой она оказалась в boot).

Для других eMMC, кроме перечисленных Samsung, восстановление firmware eMMC (вывод из boot) пока не предоставляется возможным. При этом нужно учитывать что Hynix и Sandisk падают в boot при значительном износе ячеек памяти, что значит, что долго они работать после возможного восстановления не будут.

__________________

Не задавайте глупые вопросы, и Вы не будете получать глупые ответы.

Последний раз редактировалось Layder; 08.11.2017 в 17:12 .

08.11.2017, 14:11

26 пользователя(ей) добавили плюсы

Layder

Член группы поддержки продукта

Рейтинг мнений: 980

Вес репутации: 531

Re: Инструкции по работе с EasyJTAG/EasyJTAG Plus #3

Подготовка eMMC для установки в устройство

Большинство замен eMMC производится на мобильных телефонах и планшетах. И возникает вопрос, что нужно прошить в eMMC, чтобы после её установки в плату мы получили бы или полностью работоспособное устройство, или же, чтобы хотя бы иметь возможность подключить устройство к компьютеру-ноутбуку, чтобы устройство «отдетектилось» как USB устройство.

Тема достаточно широкая, поэтому начнем с простых вещей.

Первое и основное, в микросхему eMMC необходимо записать Boot config

Boot config представляет собой 3 регистра extCSD:

1) Boot Partition [179] — регистр, который указывает, в каком разделе eMMC находится boot для загрузки

2) Bus Config [177] — ширина шины данных, и режим загрузки

3) H/W Reset Function [162] — режим управление выводом RST eMMC

Есть 4 способа это сделать:

1) из файла extcsd, сохранённого с такого же устройства;

2) из файла extcsd, сохранённого с такого же устройства, во время прошивки eMMC;

3) с помощью предустановленных вариантов;

4) вручную.

Вариант 1:

Вариант 2:

Вариант 3:

Вариант 4 (для экспертов):

Для того чтобы получить соединение с компьютером для последующего восстановления устройства с помощью ПО компьютера для устройствами на базе процессоров:

1) Mediatek (MTK)

— записать Boot cfg, и стереть eMMC (устройство определится как MTK USB Port );

или

— записать Boot cfg, и записать «Preloader» в ROM2(3) через «Write by vendor» (устройство определится как MTK Virtual VCOM Port );

или

— записать Boot cfg, и записать сохраненный бекап ROM2(3) через «eMMC General» — «Write ROM» (устройство определится как MTK Virtual VCOM Port ).

В дальнейшем большинство устройств на процессорах MTK программируются (прошиваются) компьютером через родной FlashTool для MTK.

2) Intel . У Intel есть устройства с разделом GP1 и есть без него.

— записать Boot cfg, и стереть eMMC (устройство определится как CloverView Device или другое). В этом варианте в дальнейшем потребуется записать загрузчик с помощью утилиты xfstk и дальше согласно инструкциям;

или

— записать Boot cfg, создать (при необходимости) раздел GP1, и записать в eMMC: ROM2, ROM3, GP1, и минимум примерно 300-500MB бекапа ROM1 для разных моделей. В данном варианте устройство сможет загрузится в DroidBoot , откуда его можно прошить прошивками через компьютер.

3) Qualcomm

— записать Boot cfg, и стереть eMMC (устройство определится как HS QD9008 Loader ). Для многих устройств есть сервисные прошивки для QPST в формате bin/xml, с помощью которой можно в дальнейшем восстановить устройство.

или

— записать Boot cfg, и записать часть прошивки (bootloaders, boot, recovery) через «Write by vendor — Qualcomm/Samsung», чтобы получить устройство, запускающеюся в FastBoot/Recovery и в дальнейшем записать в него прошивку через компьютер или SD карту;

или

— записать Boot cfg, и записать начало дампа ROM1 (100-500MB), в которых содержатся bootloaders, boot, recovery и другие необходимые разделы для запуска устройства в FastBoot/Recovery и в дальнейшем записать в него прошивку через компьютер или SD карту.

4) Exynos

— записать Boot cfg, и стереть eMMC, в дальнейшем такой аппарат можно восстановить только с помощью специально подготовленной SD карты под конкретное устройство;

или

— записать Boot cfg, и записать часть прошивки (bootloaders, boot, recovery) через «Write by vendor — Samsung», чтобы получить устройство, запускающеюся в FastBoot/Recovery и в дальнейшем записать в него прошивку через компьютер или SD карту;

или

— записать Boot cfg, записать ROM2 и записать начало дампа ROM1 (100-500MB), в которых содержатся bootloaders, boot, recovery и другие необходимые разделы для запуска устройства в FastBoot/Recovery и в дальнейшем записать в него прошивку через компьютер или SD карту.

5) HiSilicon

— записать Boot cfg, и записать часть прошивки (bootloaders, boot, recovery) через «Write by vendor — HiSilicon», чтобы получить устройство, запускающеюся в FastBoot/Recovery и в дальнейшем записать в него прошивку через компьютер или SD карту;

или

— записать Boot cfg, записать ROM2, начало дампа ROM1 (100-500MB), в которых содержатся bootloaders, boot, recovery и другие необходимые разделы для запуска устройства в FastBoot/Recovery и в дальнейшем записать в него прошивку через компьютер или SD карту.

6) SpreadTrum

— записать Boot cfg, и записать начало дампа ROM1 (100-500MB), в которых содержатся bootloaders, boot, recovery и другие необходимые разделы для запуска устройства в Recovery и в дальнейшем записать в него прошивку через компьютер или SD карту.

7) Broadcomm

— записать Boot cfg, и записать часть прошивки (bootloaders, boot, recovery) через «Write by vendor — Qualcomm/HiSilicon», чтобы получить устройство, запускающеюся в FastBoot/Recovery и в дальнейшем записать в него прошивку через компьютер или SD карту;

или

— записать Boot cfg, записать ROM2 и записать начало дампа ROM1 (100-500MB), в которых содержатся bootloaders, boot, recovery и другие необходимые разделы для запуска устройства в FastBoot/Recovery и в дальнейшем записать в него прошивку через компьютер или SD карту.

Более подробно в следующих сообщениях по каждому vendor будут инструкции с примерами.

p.s. в статье могут быть мелкие неточности, они будут исправляться.

Источник: www.mcrf.ru

Что такое JTAG

Ну и конечно, компания Altera предоставляет исчерпывающую документацию по использованию JTAG и BST (Boundary Scan Test ) в своих микросхемах FPGA и CPLD:

JTAG in Altera devices ( 369066 bytes )

На нашей плате Марсоход тоже есть разъем JTAG для подключения программатора UsbBlaster или ByteBlaster. Через этот разъем мы программируем нашу ПЛИС.

Попробую рассказать, что же такое JTAG своими словами.

Еще в 1980 году группа разработчиков Joint Test Action Group (JTAG ) разработала спецификацию для тестирования межсоединений на плате: » boundary-scan testing «. Позже эта спецификация была стандартизована как IEEE Std. 1149.1.

Представьте себе, что Вы разрабатываете плату скажем с 5 микросхемами и у каждой микросхемы 100-1000 контактов. Микросхемы соединены между собой тысячами соединений на плате. На заводе плата будет выпускаться партиями десятками тысяч экземпляров. Понятно, что часть плат после монтажа компонентов будет браком.

Где-то не пропаяются контакты, где-то трещина в PCB или не получилось переходное отверстие между слоями платы и так далее. Как же все таки тестировать устройства?

Вот собственно первоначальное предназначение JTAG — предоставить производителям средство тестирования собранных устройств.

Производители микросхем обязывались выпускать JTAG совместимые микросхемы. Все микросхемы на плате соединялись специальным последовательным интерфейсом из 4х сигналов TDI , TDO , TMS , TCK .

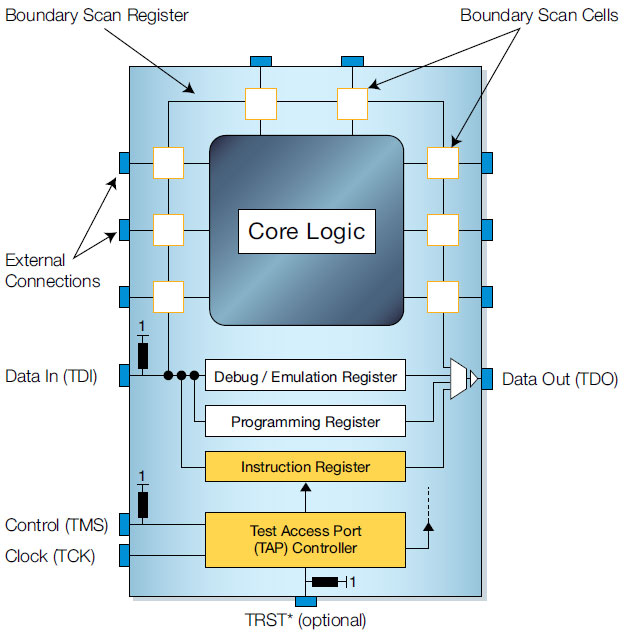

Каждый контакт микросхемы снабжается специальной логикой Boundary Scan Cell . Все эти ячейки Boundary Scan Cell всех микросхем на плате получаются объеденены в одну последовательную цепочку. Это позволяет по запросу с компьютера через интерфейс JTAG менять состояние почти любого вывода любой микросхемы, активизировать его как выход или как вход. Выход одной микросхемы выдает сигнал который передается по проводникам печатной платы и принимается входом другой микросхемы — так проверяется соединение на плате.

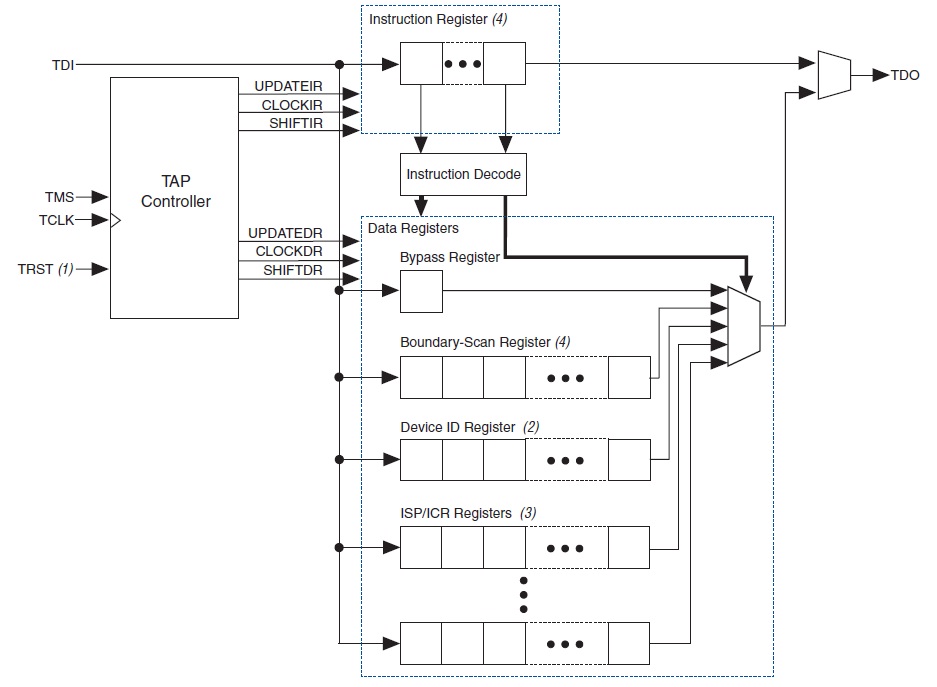

Внутри каждой микросхемы с JTAG есть специальный TAP контроллер ( Test Access Port ), который принимает последовательные команды и выполняет их. TAP контроллер управляет всеми ячейками Boundary Scan Cells . Кроме этого, через TAP контроллер можно выполнять всяческие специфические для каждой микросхемы команды.

Так, например, микросхемы компании Альтера можно: программировать CPLD, загружать образ в FPGA, считывать внутреннее состояние виртуальных пинов, использовать «внутренний цифровой осцилограф» SignalTap (для FPGA) и прочее. Для некоторых микросхем процессоров через JTAG и соответственно TAP контроллер можно вести пошаговую отладку программ, считывать состояния регистров процессора и встроенных контроллеров. В общем, довольно универсальный интерфейс.

Давайте посмотрим, как устроен TAP контроллер.

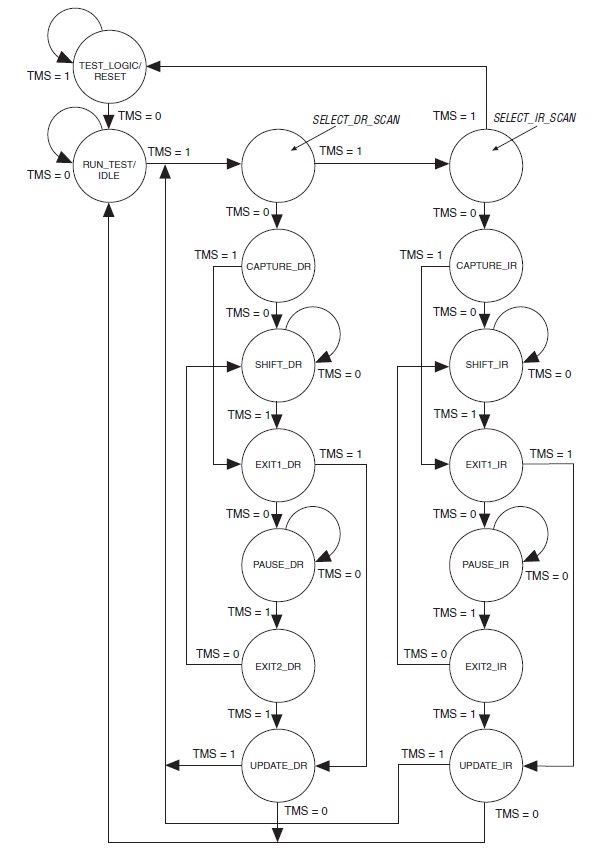

Работа TAP контроллера описывается вот таким автоматом ( state-machine ):

Кажется не понятным, но на самом деле все просто.

Интерфейс JTAG передает TAP контроллеру 3 сигнала TDI , TMS и TCK .

TCK — это тактовая частота, на которой работает интерфейс. Состояние контроллера меняется по фронту тактовой частоты TCK согласно состоянию линии TMS . Сигнал TMS определает в какое состояние переходит контроллер на следующем шаге.

Рассмотрим конкретную ситуацию.

Предположим мы находимся в начальном состоянии TEST_LOGIC/RESET . Если TMS=1 , то при каждом новом импульсе тактовой частоты TCK мы так и будем оставаться в этом состоянии.

Если на вход микросхемы TMS подать ноль, то при очередном импульсе TCK контроллер переходит в новое состояние RUN_TEST/IDLE .

Если держать TMS=0 , то мы так и будем оставаться в этом состоянии. Однако наша цель — это достичь два других возможных состояния CAPTURE_DR или CAPTURE_IR . Если мы попадем в эти состояния меняя TMS соответствующим образом, то дальше мы можем последовательно передать контроллеру либо команду (состояния SHIFT_IR ) либо данные ( SHIFT_DR ).

Передача в контроллер выполняется через сигнал TDI в одном исз состояний SHIFT_IR или SHIFT_DR . Одновременно контроллер может отдавать уже свои данные через сигнал TDO .

Обратите внимание, что из любого состояния можно вернуться в исходное состояние TEST_LOGIC/RESET если держать TMS=1 несколько тактов подряд.

Таким образом, через JTAG интерфейс в микросхему и ее TAP контроллер можно передавать разные команды и данные. Набор команд для каждых микросхем конечно свой и определяется производителем. Нас в первую очередь интересуют команды для программирования микросхем Альтера. Где бы их узнать?

На самом деле и это в общем не проблема. Среда разработки Altera Quartus может генерировать файлы в формате *.SVF. Это текстовый файл, который на специальном языке описывает последовательность действий для программирования микросхемы через JTAG/TAP . В принципе, есть некоторое описание языка SVF . Не знаю насколько это стандарт — вы можете его скачать у нас на сайте (

Описание файлов формата SVF ( 87261 bytes )

). В принципе там в текстовом файле SVF и так все довольно понятно интуитивно.

Если Вам нужен файл для программирования микросхемы Altera в формате *.SVF, то зайдите в меню среды Quartus AssignmentsDevice найдите и нажмите кнопку Device and Pin Options и увидите вот такое диалоговое окно:

Нужно установить флажок на Serial Vector Format File (*.svf).

Теперь после компиляции проекта у вас появится этот файл и вы сможете его внимательно посмотреть.

Вот фрагмент этого файла:

!

!CHECKING SILICON ID

!

SIR 10 TDI (203);

RUNTEST 93 TCK;

SDR 13 TDI (0089);

SIR 10 TDI (205);

RUNTEST 93 TCK;

SDR 16 TDI (FFFF) TDO (8232) MASK (FFFF);

SDR 16 TDI (FFFF) TDO (2AA2);

SDR 16 TDI (FFFF) TDO (4A82);

SDR 16 TDI (FFFF) TDO (0C2C);

SDR 16 TDI (FFFF) TDO (0000);

Из этого можно понять, что для того что бы проверить ID (тип) микросхемы перед прошивкой нужно:

- передать в регистр команд IR 10ти битное число 0x203;

- выждать паузу 93 такта;

- передать данные в регистр DR из 13ти бит 0x0089;

- передать в регистр команд IR десятибитное число 0x205;

- выждать паузу 93 такта;

- передавая 5 раз 16ти битное число 0xFFFF одновременно принимаем с TDO собственно ID 0x8232, 0x2aa2, 0x4A82, 0x0c2c и 0x0000

Вот эта последовательность и есть ID микросхемы платы Марсоход EPM240T100C5

Источник: marsohod.org

Интерфейс JTAG? — Это очень просто

Многие знакомы со словом «JTAG», но знакомство это скорее всего поверхностное. В этой статье я хочу перевести Вас на новый уровень, так сказать «во френдзону». Возможно, для многих я не открою ничего нового, но надеюсь тем, кто давно хотел ознакомиться, будет интересно почитать. Итак, от винта.

Введение

В 1985 сформировалась группа производителей электроники — JTAG (Joint Test Action Group). Для решения проблем тестирования в 1990 был выдвинут промышленный стандарт — спецификация IEEE Std 1149.1-1990 (IEEE Standard Test Access Port and Boundary-Scan Architecture). В этом же году Intel вывел в свет первый процессор с JTAG — 80486. С тех пор стандарт постоянно модифицируется и, в данный момент, последняя версия датируется 2013 годом.

«А какие же это проблемы с тестированием?»,- спросите Вы. Ну как же! Мало удовольствия прыгать с осциллографом по выводам микросхемы, особенно если их много больше двух!

Стандарт позволяет значительно упростить жизнь за счет встраивания специальной архитектуры в современные чипы, обеспечивающей доступ к выводам (точнее, к специальным блокам ввода-вывода) с помощью 4-х проводного последовательного интерфейса. Эта архитектура позволяет не только контролировать их состояние, но и управлять ими. Таким образом можно обойтись без громоздких пробников с физическим контактом и насладиться всей прелестью этапа отладки цифровых микросхем или устройств уровня печатной платы.

Стандарт используют как для целей внутрисхемного программирования и отладки программ, так и при работе с корпусированными микросхемами. Он же используется для проверки на качество припайки микросхем к плате, межплатного и внутристоечного монтажа плат и блоков. Также надо сказать ему спасибо за восстановление закирпиченных по неосторожности мобильных устройств.

И как же работает?

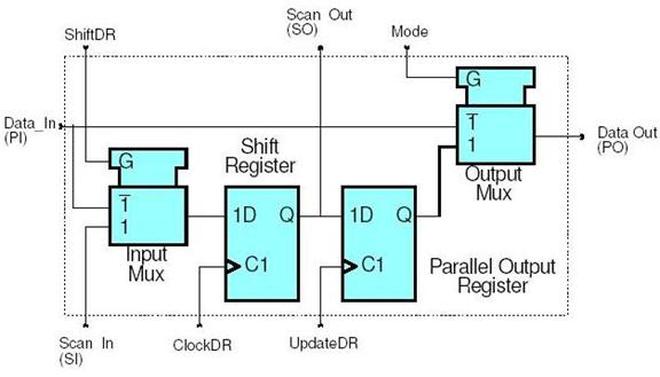

Механизм граничного сканирования заключен, всего лишь, в сдвиговом регистре (Boundary Scan), подключенном между выводами микросхемы и ядром, и мультиплексоре который подключает в нужный момент этот регистр. Каждому конкретному выводу соответствуют так называемые «ячейки».

В состав ячейки входит один триггер регистра граничного сканирования и мультиплексора выбора данных. Ячейки могут быть разных типов в зависимости от вывода микросхемы и команд интерфейса, т.е. зависит от производителя той или иной микросхемы. Производители не придерживаются строго стандарта и, поэтому, развелось множество модификаций.

На рисунке представлена одна из разновидностей ячейки. PI, PO — параллельные вход и выход, SI,SO — последовательные.

Сигналы на регистр микросхемы попадают через мультиплексор, который позволяет считывать как состояния выводов ядра микросхемы (инструкция INTEST), так и данные, поступающие извне на сдвиговый регистр (инструкция EXTEST). Разновидности инструкций и их функциональность опять же меняются от желаний производителя, но существуют так называемые обязательные:

- EXTEST — инструкция, позволяющая за счет установки логических значений на рабочих контактах электронных компонентов проверить внешние цепи, имеющие непосредственное отношение к тестируемому компоненту.

- INTEST — инструкция обеспечивает возможность установки логических значений внутри микросхемы, то есть на входах ядра, тем самым проверяя его.

- SAMPLE_PRELOAD — позволяет тестировать ядро электронного элемента в статическом режиме, устанавливая значения логических уровней на границе его выходных буферов.

- BYPASS — инструкция, при которой наш регистр граничного сканирования «схлопывается» в один триггер. При этом данные со входа (TDI) на выход (TDO) передаются с задержкой в один такт частоты синхронизации интерфейса (TCK). Этот режим позволяет эффективно использовать возможности последовательного интерфейса при организации длинных последовательно объединенных цепочек.

- IDCODE — инструкция выдвигает на выход значение встроенного 32-битного регистра с идентификаторами производителя, модели и версии устройства.

Сигнальные линии интерфейса

Как уже говорилось выше, интерфейс JTAG имеет следующие сигнальные линии:

- TDI — Test Data Input — сигнал данных на вход, данные задвигаются по переднему фронту TCK.

- TDO — Test Data Output — выход последовательных данных JTAG, выдвигаются по заднему фронту TCK, должен находиться в третьем состоянии — Z — когда данные не передаются.

- TMS — Test Mode Select — сигнал управления TAP — контроллером.

- TRST — Test Reset — не всегда есть, так как ресета можно добиться удерживая некоторое время TMS = 1, активный уровень сигнала — 0.

- TCK — Test Clock — тактовая частота.

TAP — контроллер

Мы добрались до самой сути JTAG, а именно — управляющий работой автомат. С его помощью собственно и живет всё вокруг. Автомат имеет 16 состояний. Управление интерфейсом осуществляется путем воздействия на автомат посредством сигнала TMS. Переходы происходят по переднему фронту сигнала TCK. Чтение и запись данных происходят одновременно.

Ниже привожу иллюстрацию работы, взятую из документации микросхем фирмы Altera.

Диаграмма переходов автомата, управляющего режимами TAP

- Test-Logic-Reset – исходное состояние;

- Run-Test/Idle – переходное состояние контроллера при выполнении тестов или ожидании следующей

- команды;

- Select-IR, Select-DR – состояние, после которого будет производиться тестирование команд, данных;

- Capture-IR, Capture-DR – состояние приёма команд, данных;

- Shift-IR, Shift-DR – состояние сдвига команд, данных;

- Exit1-IR, Exit2-IR – выход из режима работы с командами;

- Exit1-DR, Exit2-DR – выход из режима работы с данными;

- Pause-IR, Pause-DR – состояние паузы;

- Update-IR, Update-DR – состояние перезаписи данных в выходные регистры.

Исходное состояние, в котором находится автомат после включения, это Test-Logic Reset. Пока сигнал TMS имеет значение «лог.1», состояние автомата остается неизменным. В этом состоянии, по умолчанию, выбрана инструкция IDCODE или BYPASS.

Сигнал сброса TRST не является обязательным, поэтому для сброса автомата в исходное состояние применяют следующую процедуру. Необходимо подать на вход TMS сигнал высокого уровня и удерживать его не менее 5 тактов частоты TCK. Если сигнал TMS будет установлен хостом в низкий уровень, то автомат перейдёт к состоянию Run-Test/Idle (активное состояни, в котором ничего не происходит).

Обычно из этого состояния можно перейти в состояние Select-IR, для того чтобы загрузить в контроллер новую инструкцию. Но если на вход сигнала TMS подействует не сигнал, подаваемый от хоста, а помеха низкого уровня, то, как и в предыдущем случае, автомат перейдёт в состояние Run-Test/Idle. Если же кратковременная помеха (длительностью не более одного периода синхрочастоты) прекратится, то автомат через три такта снова вернётся в исходное состояние – Test-Logic Reset.

Чтобы загрузить в контроллер новую команду, надо из состояния Run-Test/Idle перевести автомат в состояние Select-IR, Capture-IR, Shift-IR. Затем необходимо «продвинуть» в цепочку данных новую команду, а потом перевести автомат через состояния Exit1-IR, Update-IR и снова в Run-Test/Idle. Логика работы с данными такая же. Нужно учитывать, что сигнал высокого уровня при переходе из состояний Shift-IRDR подается вместе с последним битом информации.

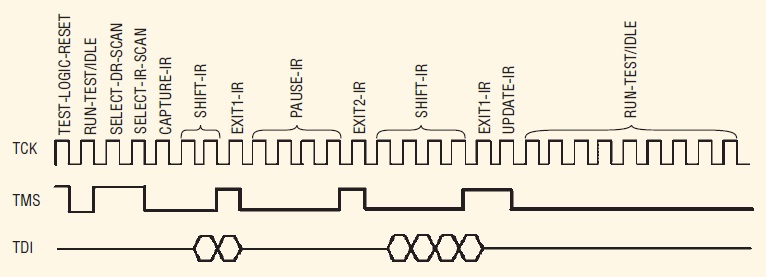

Диаграмма сигналов при выполнении переходов для загрузки команды

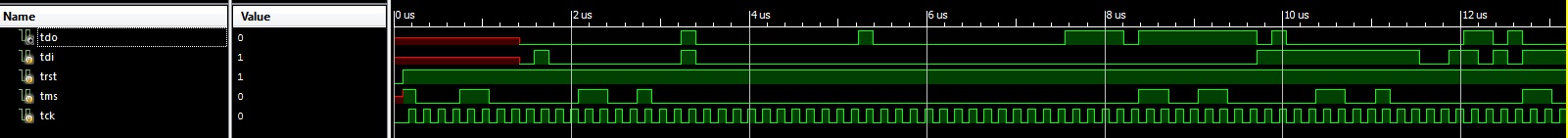

Если используя специализированный САПР написать код работы JTAG на Verilog, то результирующая диаграмма будет выглядеть примерно так:

Сылка на дропбокс, картинка в полный размер

Наконец можно показать полную структурную схему устройства JTAG и Вы вполне должны в ней разобраться:

… И в заключение.

Использование JTAG и технологии граничного сканирования в микросхеме, на плате или в устройстве добавляет стоимость и увеличивает время разработки проекта. Но, всё же эти затраты легко окупаются при проведении тестирования, которое обеспечивается на каждой стадии цикла жизни изделия. То, что было первоначально разработано как производственный испытательный инструмент, используется до начала производства, во время серийного производства и после производства, то есть на этапе эксплуатации конечным пользователем. Кроме непосредственно граничного тестирования, проектировщики используют технологию JTAG для того, чтобы производить самотестирование (BIST) (в тех компонентах, где оно реализовано) и загружать внутренние значения в регистры устройства или программировать микросхемы ПЗУ. Тесты, которые были разработаны и использованы на этапе проектирования, могут быть переданы производству, для того чтобы обеспечить дополнительное снижение стоимости и времени на проверку изделий при выходном контроле.Основные положительные эффекты от применения технологии JTAG в производственной фазе – экономия времени при разработке испытательных тестов, улучшенный «охват» тестируемого изделия при поиске ошибки и диагностировании и улучшенная производительность испытаний при одновременном уменьшении времени испытания.

Применение граничного сканирования при эксплуатации изделия также даёт определённый положительный эффект. Отказы при эксплуатации часто происходят из-за структурных отказов, которые вызываются повышенной температурой, влажностью, вибрацией. Используя граничное сканирование, техники имеют возможность быстро проверить изделие на структурные ошибки вплоть до уровня компонентов без трудоёмкого исследования или возвращения платы изготовителю на завод.

- jtag

- boundary-scan

- интерфейсы тестирования

Источник: habr.com

Что такое JTAG и как это применить для тестирования печатных плат?

JTAG – это нечто большее, чем просто отладка и перепрограммирование микросхем

Если Вы применяли какие-либо инструменты, использующие JTAG, то Вы уже знакомы с этим интерфейсом. Например, процессоры часто используют JTAG для доступа к своим отладочным функциям, также все ПЛИС используют JTAG для перепрограммирования.

JTAG – это НЕ ТОЛЬКО отладка процессоров.

JTAG – это НЕ ТОЛЬКО программирование ПЛИС/CPLD.

Название JTAG чаще всего ассоциируется с инструментами отладки и перепрограммирования микросхем. Однако, в этих инструментах реализована только часть возможностей JTAG.

Эта часть возможностей, известная под названием Test Access Port или, сокращённо, TAP, является частью стандарта IEEE Std. 1149.1. Этот стандарт был разработан для тестирования сборок печатных плат (Printed Circuit Board Assemblies – PCBA) без необходимости доступа на так называемом «низком» (физическом) уровне, который требуется для анализа «сложных» случаев. Стандарт также не предусматривает разработку и использование специфических функциональных тестов. Изначально TAP был разработан только для взаимодействия с дополнительными регистрами, специально вставляемыми в микросхему с целью реализации данного метода тестирования.

Однако достаточно быстро производители микросхем заметили потенциал использования TAP и для других целей, например, для доступа к регистрам, предназначенным для отладки и перепрограммирования микросхем.

Теперь в микросхемы добавляется специальный регистр для тестирования через JTAG под названием Boundary Scan Register (BSR). Как и подразумевает название этого регистра, отдельные его части (или, по-другому, ячейки (Cells)) являются «пограничными» для микросхемы, так как располагаются между функциональным ядром и контактами корпуса микросхемы. По этой причине тестирование через JTAG часто называют пограничным сканированием (boundary scan).

Как технология пограничного сканирования, реализуемая стандартом JTAG, используется для тестирования печатных плат?

Ячейки регистра пограничного сканирования (Boundary Scan Register) могут работать в одном из двух режимов: 1) функциональный режим – ячейки не влияют на работу прибора, прибор работает в своём обычном виде; 2) тестирующий режим – ячейки отсоединяют функциональное ядро микросхемы от контактов корпуса. Тестирующий режим используется для управления значениями на контактах корпуса микросхемы (и в соответствующих цепях печатной платы), а также для считывания значений с подключённых цепей печатной платы.

Отключение функционального ядра микросхемы существенно упрощает разработку тестов, так как использование пограничного сканирования (boundary scan) позволяет не разрабатывать программу для микропроцессора или прошивку для ПЛИС и не включать прибор в «рабочем» режиме. Механизм управления и наблюдения за контактами корпуса микросхемы через четырёх-контактный TAP, JTAG интерфейс позволяет получить низкоуровневый доступ к контактам микросхемы для физического тестирования печатной платы.

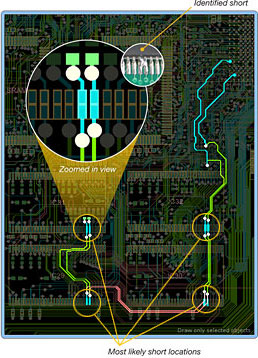

Существует два способа тестирования печатной платы при помощи пограничного сканирования (boundary scan). Первый способ – тест соединений (connection test). Он даёт хорошее покрытие, особенно для поиска таких неисправностей, как замыкания. Этот способ использует только возможности микросхемы с поддержкой JTAG, при этом тестируются соединения (например, пропайки) и цепи, а в случае применения системы XJTAG, тестируются ещё и логические функции платы. Второй способ – использование микросхемы с поддержкой JTAG для взаимодействия с микросхемами без поддержки JTAG, такими как DDR RAM или Flash память.

Что такое тест соединений (connection test) через JTAG?

Тест соединений (connection test) проверяет, соответствует ли изготовленная печатная плата исходному проекту, а также наличие на ней не предусмотренных проектом разрывов цепей или лишних замыканий.

Если согласно проекту какие-то контакты микросхемы должны быть соединены где-то на плате, то можно проверить факт наличия соединения, подавая значения на один из контактов и считывая с других. Если согласно проекту контакты микросхемы НЕ соединены, то можно проверить, нет ли между ними лишнего замыкания, подавая на один из них значения и проверяя, что на остальные это не влияет.

Кроме того, тест соединений (connection test) позволяет обнаружить отсутствие нужных подтягивающих резисторов, и «залипания» сигналов. Это также делается путём выставления на контактах определённых значений и сравнения считанных значений с заданной таблицей истинности.

Система XJTAG на основе нетлиста печатной платы и информации, считанной с поддерживающих JTAG микросхем, полностью автоматически генерирует тестовые вектора для проведения теста соединений (connection test) всей платы.

Что же делать с остальными микросхемами на плате, которые не поддерживают JTAG?

Как правило, основные микросхемы на плате, такие как процессоры и ПЛИС, поддерживают JTAG, но существует множество вспомогательных микросхем, которые JTAG не поддерживают. Как пример можно привести такие микросхемы, как ЦАП, АЦП, DDR, SDRAM, SRAM, Flash, Ethernet контроллеры, температурные сенсоры, генераторы частот и многое другое.

Тест соединений (connection test) позволяет проводить тестирование на замыкания цепей между микросхемами с поддержкой JTAG и микросхемами без поддержки, при этом достигается хорошее покрытие. Однако протестировать обрывы в таких цепях уже не получится.

С целью тестирования на наличие обрывов цепей между микросхемами с поддержкой JTAG и микросхемами без таковой, требуется использовать так называемые функциональные тесты. Если функциональные тесты пройдены, то это означает, что обрывов быть не может. Функциональные тесты могут быть как очень простыми, например, включение светодиода и ожидание подтверждения от оператора, что светодиод действительно загорелся, так и посложнее, например, запись данных в память, считывание их же и сравнение считанных данных с ожидаемыми.

Насколько сложно подготовить JTAG тесты?

При помощи библиотеки тестов для стандартных микросхем без поддержки JTAG, поставляемой с системой XJTAG, возможна подготовка и запуск набора функциональных тестов без необходимости программирования. Библиотека тестов содержит тесты как для простых элементов, таких как резисторы и буферные элементы, так и для сложных микросхем, таких как память DDR3 и так далее.

Т.к. пограничное сканирование (boundary scan) отключает контакты корпуса микросхемы от функционального кремниевого ядра, единая тестовая модель может быть использована для управления периферийными микросхемами вне зависимости от того, какая микросхема с поддержкой JTAG использована.

Как правило, в печатную плату не требуется вносить никаких изменений, так как большинство плат уже содержат JTAG контакты для отладки процессоров или программирования ПЛИС.

Что ещё нужно для использования микросхем с поддержкой JTAG?

Для тестирования печатной платы при помощи пограничного сканирования (boundary scan) требуется для каждой микросхемы с поддержкой JTAG скачать с сайта производителя микросхемы так называемый BSDL-файл – Boundary Scan Description Language. Это текстовый файл, описывающий назначения ножек корпуса микросхемы.

Используется ли JTAG тестирование в основном на производстве?

Не совсем. Одним из важнейших преимуществ тестирования через пограничное сканирование (boundary scan) является тот факт, что из дополнительного оборудования требуется только JTAG контроллер. Другие технологии тестирования, такие как летающие щупы (flying probe), рентгеновское сканирование, многозондовое тестирование (bed-of-nails) и так далее требуют наличия дорогостоящего оборудования, которое не всегда доступно.

Использование пограничного сканирования (boundary scan) при первом тестировании позволяет проводить тестирование более уверенно, так как не требует включения платы в основной режим работы и даже может быть выполнено ещё до окончания разработки «прошивки». Эти же тесты, разработанные при проектировании, могут быть использованы и на производстве.

Почему следует использовать пограничное сканирование через JTAG для тестирования печатных плат?

BGA

С увеличением доли микросхем, реализованных в корпусе BGA (Ball Grid Array), применение традиционных систем тестирования печатных плат, таких как многозондовое тестирование (bed-of-nails) или летающие щупы (flying probe) становится всё более ограниченным, так как «внутренние» контакты физически недоступны.

Пограничное сканирование (boundary scan) на основе JTAG при помощи простого «четырёхконтактного» интерфейса позволяет произвольно управлять контактами корпуса микросхемы с поддержкой JTAG, в том числе считывать значения, не имея к контактам физического доступа.

Стенд

В процессе проектирования и отладки временны́е и денежные затраты на разработку/приобретение испытательных/отладочных стендов могут быть очень существенными, а в некоторых случаях и превышать затраты на само проектирование. Во многих случаях использование пограничного сканирования (boundary scan) позволяет вообще отказаться от применения испытательного стенда, а в остальных случаях подойдет и значительно более простой и дешёвый стенд.

Малые партии

В случае, когда у компании имеется много проектов плат, выпускаемых малыми партиями, задача удешевления тестового оборудования особенно актуальна. Единственно приемлемым вариантом в данном случае является покупка системы «летающие щупы» (flying probe), но если цена при этом делится на все проекты, то временны́е затраты на подготовку теста для каждого проекта остаются неприемлемыми. Использование пограничного сканирования (boundary scan) позволяет ускорить подготовку теста для каждого проекта, при том, что покупка дорогостоящего тестового оборудования теперь не требуется.

Стоимость разработки теста

Так как разные микросхемы (процессоры и ПЛИС) взаимодействуют с периферией разными способами, разработка традиционного функционального теста отдельно для каждой платы является очень затратной. Пограничное сканирование (boundary scan) существенно сокращает стоимость разработки тестов благодаря упрощённому способу управления контактами корпуса микросхемы для взаимодействия с остальными компонентами на плате. А унифицированный интерфейс JTAG позволяет формировать отдельные тесты как библиотечные элементы и использовать их в разных проектах вне зависимости от применяемых микросхем с поддержкой JTAG.

И для тестирования и для программирования

JTAG часто применяется для программирования микросхем (ПЛИС) на плате в процессе производства. А если к программированию дополнительно добавить тестирование платы через так называемое пограничное сканирование (boundary scan), то получится существенно сэкономить время и упростить производство.

Использование на производстве тех же тестов, которые применялись при проектировании

Обычно для тестирования изделий на производстве применяется большое дорогостоящее оборудование. Всё, что требуется для применения пограничного сканирования (boundary scan) через JTAG – это контроллер XJLink, размерами сопоставимый с компьютерной мышью.

Удобная диагностика неисправностей

Пограничное сканирование (boundary scan) через JTAG, в отличие от специально разработанных функциональных тестов, позволяет получать информацию о точном месте возникновения неисправности, что очень помогает при восстановлении платы. А применение системы XJTAG ещё и позволяет визуализировать место неисправности на плате и указать точное место в принципиальной схеме.

Восстановление нерабочих плат, где функциональные тесты бессильны

Пограничное сканирование (boundary scan) через JTAG можно использовать на плате, где не работает ничего, кроме самого JTAG интерфейса. Если плата не включается, то провести традиционные функциональные тесты не получится. Простейшая неисправность в таких элементах на плате, как память или генератор синхросигнала не позволят применить функциональный тест, но легко обнаруживается при помощи JTAG.

Ещё статьи

Концепция применения JTAG

Посмотрите, на что способен JTAG (Английский)

Источник: www.xjtag.com