ПЛИС — это программируемые логические интегральные схемы.

Общие сведения о ПЛИС

Первые ПЛИС, то есть, программируемые логические интегральные схемы, можно было сконфигурировать простым заданием положения всех электронных ключей вручную. А в настоящее время программируемые логические интегральные схемы (ПЛИС) повсеместно используются при формировании цифровых систем различного назначения. Ранее совокупность дискретных цифровых логических микросхем различных серий достаточно длительный период времени являлись основой элементной базой для формирования цифрового оборудования. В состав таких совокупностей входило очень большое число различных микросхем, которые выполняли, как основные логические функции, то есть И, ИЛИ, НЕ, так и функции типовых цифровых устройств, например, триггеров, регистров, счетчиков, мультиплексоров, дешифраторов и тому подобное.

Основным недостатком дискретных логических микросхем является то обстоятельство, что для создания конечного продукта, так или иначе, требуется большое число микросхем, и, следовательно, это подразумевает значительное количество внешних соединений. В результате возрастает уровень сложности конструкции, увеличиваются габариты печатных плат и снижается степень надежности.

Лекция №1 «Что умеют FPGA и зачем они нужны?»

Следует также подчеркнуть, что в таком случае достаточно сложно создать устройства, которые обладают высокой тактовой частотой. Однако иногда возникает необходимость в проектировании цифровых устройств, требующих не типовой схемотехнической структурной организации построений и не рассчитанных на крупносерийное производство. В таком случае является вполне целесообразным применение ПЛИС.

Применение ПЛИС, которые обладают даже средним уровнем интеграции, может выступать как замена, как правило, примерно пятнадцати стандартных интегральных микросхем. При этом такая замена способна позволить значительно минимизировать размеры устройства, уменьшить потребляемую мощность и увеличить надежность. Другим существенным преимуществом использования ПЛИС можно считать кардинальное сокращение времени и финансовых вложений в проектные работы, а также появление возможности выполнять оперативную модификацию и отладку оборудования.

«Программирование ПЛИС»

Готовые курсовые работы и рефераты

Решение учебных вопросов в 2 клика

Помощь в написании учебной работы

По данной причине ПЛИС повсеместно применяется при проектных работах по созданию стендового оборудования, на стадии проектирования и реализации опытной партии новых видов продукции, а также, для того чтобы эмулировать схемы, подлежащие последующему осуществлению на другой элементной базе. На базе ПЛИС принято реализовывать микропрограммные автоматы, позволяющие применять наилучшие алгоритмы, выполняющие обработку сигналов, таких как:

- Алгоритмы, которые способны реализовать цифровую фильтрацию, в том числе и алгоритмы нелинейной, оптимальной, адаптивной фильтрации и так далее.

- Алгоритмы, которые базируются на применении ортогонального преобразования, например, на быстром преобразовании Фурье.

- Алгоритмы, реализующие кодирование и декодирование, а также процессы модуляции и демодуляции, в том числе, которые предназначены для сложных сигналов, а именно, псевдослучайных, хаотических и других.

- Алгоритмы, которые реализуют разные интерфейсы и типовые протоколы обмена и передачи данных.

- Алгоритмы, которые предназначены, для того чтобы уплотнить телефонные сигналы в технике связи.

Программирование ПЛИС

В обобщенном варианте процесс создания цифровых схем на базе ПЛИС включает следующие основные этапы:

1. ПЛИС (FPGA) Введение

- Выбор ПЛИС, позволяющий спроектировать необходимую схему исходя из ее объема и быстродействия.

- Разработка схемы и ее занесение в программу с помощью специального языка или универсального схемного редактора.

- Моделирование схемы, позволяющее выполнить проверку достоверности ее работы.

- Размещения схемы на кристалле и реализация необходимых связей.

- Преобразование исследуемой схемы в битовую последовательность.

- Загрузка данной последовательности в кристалл, то есть, практическая реализация программирования ПЛИС.

Сегодня проектирование конфигурационной прошивки для ПЛИС, которая настраивает ее на исполнение требуемого заказчику функционального набора, является процессом сложным и, как указано уже выше, многоэтапным. Начинать его следует с описания функциональности устройства на языке высокого уровня. Наиболее часто такими языками являются Verilog или VHDL, но в последнее время таким языком может быть и C/C++, а так же итоги работы программ, подобных Matlab/Simulink или LabView.

Термин программирование здесь может считаться достаточно условным, так как под ним понимается процесс, который приводит в конечном итоге к некоторой функциональной конфигурации ПЛИС, в отличие от программирования для процессорных систем, в которых программированием является задание на определенном языке очередности исполнения операций. Это означает, что главные языки, применяемые, для того чтобы сформировать требуемую функциональность ПЛИС, а именно, Verilog/SystemVerilog и VHDL, строго говоря, не могут считаться языками программирования. Поэтому их принято называть языками проектирования аппаратуры HDL (Hardware Design Language).

Невзирая на очевидный сдвиг в сторону проектирования высокого уровня, в полной мере потенциал программируемой логики может быть раскрыт лишь на классических языках проектирования аппаратуры. Как указано выше, таких языков известно всего два, а именно, Verilog/SystemVerilog (разработан 1984/2002 годы) и VHDL (разработан 1983 году). Данные языки являются полностью функционально эквивалентными, но обладают совершено разным синтаксисом. Общими чертами HDL-языков являются следующие моменты:

- Языки имеют синтезируемое и не синтезируемое подмножество операторов. Именно синтезируемые операторы, описывающие функциональность реальной аппаратуры отличают HDL-языки от обычных языков программирования. В то время как не синтезируемое подмножество используется для симуляции и тестирования и мало отличается от алгоритмических языков программирования.

- Языки используются для описания параллельно выполняющихся действий.

Источник: spravochnick.ru

Записки программиста

ПЛИС (Программируемая Логическая Интегральная Схема) — это интегральная схема, предназначенная для построения цифровых цепей из описания на специальном языке программирования. Другими словами, ПЛИС представляет собой чип, как бы содержащий в себе кучу элементов наподобие 74HCxx. Какие именно это будут логические элементы, какие между ними будут связи, и какие связи будет иметь получившаяся схема с внешним миром, определяется на этапе программирования ПЛИС.

Примечание: Насколько я смог выяснить, в русском языке на сегодняшний день термины ПЛИС и FPGA (Field-Programmable Gate Array, Программируемая Пользователем Вентильная Матрица), принято считать взаимозаменяемыми, что будет использовано далее по тексту. Однако стоит знать о существовании и альтернативной точки зрения, согласно которой FPGA (ППВМ) является одной из разновидностей ПЛИС (PLD, Programmable Logic Device).

Основные сведения об FPGA

Для программирования FPGA используются языки описания аппаратуры (HDL, Hardware Description Language). Среди них наибольшей популярностью пользуются Verilog (и его диалекты, в частности SystemVerilog), а также VHDL. Языки во многом похожи, но имеют разный синтаксис и различаются в некоторых деталях. Если Verilog — это такой C мира описания аппаратуры, то VHDL — соответственно, Pascal.

Насколько мне известно, VHDL несколько менее популярен, в частности, из-за его многословности по сравнению с Verilog. Из преимуществ VHDL (или недостатков, кому как) можно назвать строгую статическую типизацию. Verilog же иногда допускает неявное приведение типов. Если продолжать аналогию с C и Pascal, языки различаются не настолько сильно, чтобы не выучить их оба.

На данный момент лидирующими производителями FPGA являются компании Altera (сейчас принадлежит Intel) и Xilinx. По информации из разных источников, вместе они контролируют не менее 80% рынка. Из других игроков стоит отметить Actel (куплена Microsemi), Lattice Semiconductor, Quicklogic и SiliconBlue. С железом от Xilinx можно работать только из среды разработки от Xilinx (называется Vivado), а среда разработки от Altra (называетя Quartus) понимает только железо от Altera. То есть, полный вендор лок, и выбирая конкретную FPGA для своего проекта, вы автоматически выбираете и инструменты разработки соответствующего производителя, их техническую поддержку, документацию, условия лицензирования софта, политику касаемо прекращения поддержки железа, и так далее.

FPGA часто используются в задачах, где некие вычисления хочется существенно ускорить, реализовав их прямо в железе. Например, FPGA нашли широкое применение в области обработки сигналов, скажем, в осциллографах, анализаторах спектра, логических анализаторах, генераторах сигналов, Software Defined Radio и даже некоторых мониторах.

В частности, в LimeSDR используется Altera Cyclone IV, а в осциллографе Rigol DS1054Z стоит Xilinx Spartan-6, а также ProASIC 3 от компании Actel. Еще из применений, о которых я слышал, могу назвать компьютерное зрение, распознавание речи и биоинформатику. Есть и другие проекты, в частности по разработке веб-серверов и СУБД, работающих на FPGA [PDF]. Но, насколько мне известно, это направление все еще остается сильно экспериментальным.

Xilinx или Altera?

Как говорится, лучший Linux тот, который использует ваш знакомый гуру по Linux.

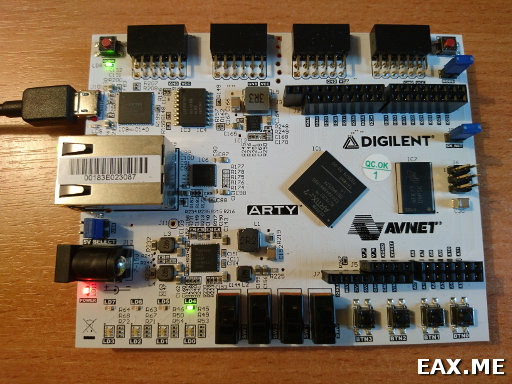

Мой знакомый гуру по FPGA в лице Дмитрия Олексюка посоветовал начать с девборды Arty Artix-7 от компании Digilent. Используемой в ней FPGA является Artix-7 от Xilinx. Сам Digilent не производит доставку в Россию, но устройство доступно и на Aliexpress, хотя и с заметной наценкой (официальная цена составляет 99$). Также его продают на eBay. Это довольно мощная плата, которая, тем не менее, стоит вполне адекватных денег.

Fun fact! Если вам просто хочется попрограммировать на Verilog или VHDL, строго говоря, покупать какую-либо плату с FPGA не требуется. Первое время можно ограничиться симулятором, работа с которым будет рассмотрена далее.

Из интересных особенностей платы можно назвать расположение гнезд совместимым с Arduino-шилдами способом. Также в комплекте с платой идет вкладыш, по которому можно получить лицензию на Vivado, открывающую все его возможности. Лицензия действует один год с момента активации, а также привязана к одному компьютеру по типу ОС и MAC-адресу.

По доставке. Я слышал, что устройства с FPGA на борту имеют большие шансы не пройти таможню. Магазин на Aliexpress, ссылку на который я привел выше, доставляет платы в Россию через курьерскую службу СПСР. Для прохождения таможни потребовалось заполнить онлайн-форму с паспортными данными (только данные, без фото) и контактным телефоном, как этого требует текущее российское законодательство. После этого плата была доставлена курьером прямо до двери без каких-либо вопросов.

Установка Vivado

Среда разработки Vivado доступна для скачивания на сайте Xilinx. Будьте морально готовы к тому, что перед скачиванием вам придется пройти регистрацию и заполнить довольно подробную форму о себе. Скачиваем архив под названием «Vivado HLx 2017.2: All OS installer Single-File Download». Не перепутайте случайно с каким-нибудь «Vivado Lab Solutions», это совершенно не то, что нужно. Архив весит более 20 Гб, поэтому запасаемся терпением.

Распаковываем архив, запускаем инсталлятор. Ставим Vivado HL System Edition. Полная его версия займет на диске 47 Гб. Лично я снял галочку напротив Software Development Kit и оставил поддержку только 7 Series устройств, что уменьшило размер до 12 Гб. Забегая немного вперед отмечу, что такой конфигурации оказалось вполне достаточно.

Перед запуском Vivado нужно добавить в него поддержку Arty Artix-7, так как из коробки он ничего об этой плате не знает. Делается это как-то так:

cd ~ / opt / xilinx / Vivado / 2017.2 / data / boards / board_files

wget https: // github.com / Digilent / vivado-boards / archive / master.zip

unzip master.zip

mv vivado-boards-master / new / board_files /* . /

rm -r vivado-boards-master

rm master.zip

Также скачиваем отсюда и сохраняем куда-нибудь файл Arty_Master.xdc. Он понадобится нам далее. Файл содержит описание находящихся на плате светодиодов, переключателей и так далее. Без него поморгать светодиодами на Verilog будет непросто.

Первый проект на SystemVerilog

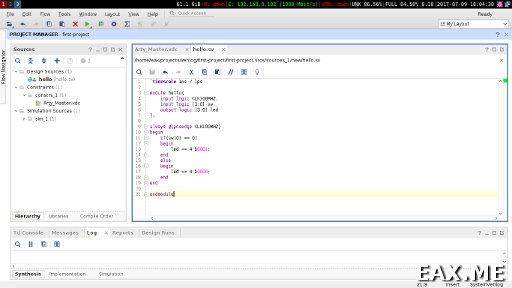

В Vivado говорим File → New Project… В качестве типа проекта выбираем RTL Project, ставим галочку Do not specify sources at this time. В диалоге выбора типа платы находим в списке Arty.

Первым делом добавляем к проекту скачанный ранее XDC файл. Копируем его в каталог с проектом. Затем говорим File → Add Sources… → Add or create constraints → Add Files, находим копию файла, жмем Finish. В дереве файлов проекта (Sources) в группе Constraints появится файл Arty_Master.xdc, или как вы там назвали копию. Открываем его и раскомментируем все строчки в группах Clock signal, Switches и LEDs.

Далее говорим File → Add Sources… → Add or create design sources → Create File. В типе файла выбираем SystemVerilog, в имени файла вводим что-нибудь вроде hello. Говорим Finish. Далее появится диалог Define Module, который предложит накликать интерфейс модуля. Диалог довольно бесполезный, потому что то же самое удобнее сделать прямо в коде, так что жмем Cancel.

В дереве исходников находим новый файл hello.sv, он будет в группе Design Sources. Открываем и пишем следующий код:

`timescale 1ns / 1ps

module hello (

input logic CLK100MHZ ,

input logic [ 3 : 0 ] sw ,

output logic [ 3 : 0 ] led

) ;

Если все было сделано правильно, на этом этапе Vivado у вас будет выглядеть как-то так (кликабельно, PNG, 71 Кб):

Компиляция программы осуществляется в два этапа — синтез (synthesis) и имплементация (implementation). На этапе синтеза программа транслируется в абстрактную цепь из логических вентилей и прочих элементов. На этапе имплементации принимается решение о том, как прошить эту цепь в конкретную железку.

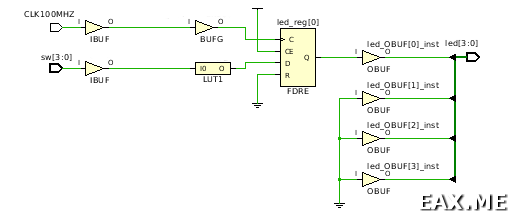

Запустим синтез, сказав Flow → Run Synthesis, или просто нажав F11. В правом верхнем углу вы увидите индикацию того, что процесс идет. Он может занимать довольно много времени, в зависимости от вашего компьютера и сложности программы. На моем ноутбуке синтез приведенной выше программы выполнился где-то секунд за 10. Если теперь сказать Flow → Open Synthesized Design, то можно увидеть красивую картинку вроде такой:

Настало время прошить нашу плату. Говорим Flow → Run Imlementation, затем Flow → Generate Bitstream. Подключаем плату к компьютеру по USB, в Vivado говорим Flow → Open Hardware Manager → Open target → Auto Connect → Program device. Потребуется указать путь к bit-файлу. У меня он был следующим:

./first-project.runs/impl_1/hello.bit

Говорим Program. Теперь на плате горит светодиод LD4, если переключатель SW0 опущен (см приведенную выше фотографию платы). Если же переключатель поднят, светодиод не горит. Простенько, конечно, но это же «hello, world», чего вы ожидали? 🙂

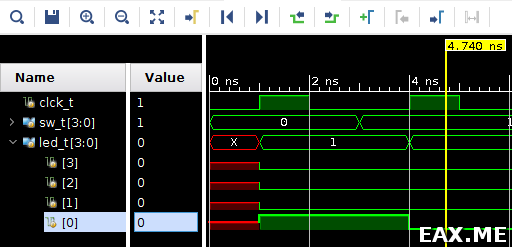

Симуляция

Симуляция — это виртуальное выполнение кода на Verilog или VHDL прямо на вашем компьютере, безо всяких там ПЛИС’ов. Это одновременно и отладочный инструмент, и своего рода фреймворк для покрытия кода тестами.

При знакомстве с симуляцией первое, что я обнаружил, было то, что она у меня не работает. В логах было просто:

ERROR: [XSIM 43-3409] Failed to compile generated C file [. ]xsim_1.c.

Google по этой ошибке находил только всякую ерунду в стиле «попробуйте отключить антивирус». В итоге решить проблему помогло добавление флага -v 2 в скрипт ~/opt/xilinx/Vivado/2017.2/bin/xelab. С его помощью я выяснил, что Clang, бинарник которого Vivado таскает за собой, падает со следующей ошибкой:

/a/long/path/to/clang: error while loading shared libraries:

libncurses.so.5: cannot open shared object file: No such file or

directory

А эта ошибка и ее решение уже описаны на Arch Wiki. Лично я просто скопировал уже существующий файл из каталога Vivado_HLS:

cp ~/opt/xilinx/Vivado_HLS/2017.2/lnx64/tools/gdb_v7_2/libncurses.so.5

~/opt/xilinx/Vivado/2017.2/lib/lnx64.o/libncurses.so.5

… после чего все заработало. Итак, а теперь, собственно, пример симуляции.

По аналогии с тем, как ранее мы создавали hello.sv, создаем новый файл hello_sim.sv в группе Simulation Sources. В файле пишем следующий код:

`timescale 1ns / 1ps

module hello_sim ( ) ;

logic clck_t ;

logic [ 3 : 0 ] sw_t ;

logic [ 3 : 0 ] led_t ;

hello hello_t ( clck_t , sw_t , led_t ) ;

В дереве исходников делаем правый клик по файлу, выбираем Source Node Properties. В секции Used In снимаем галочки Synthesis и Implementation. Мы же не хотим, чтобы какие-то там тесты засоряли нашу далеко не резиновую FPGA?

Теперь говорим Flow → Run Simulation → Run Behavioral Simulation. В итоге вы увидите что-то примерно такого плана:

Можно видеть, что когда sw[0] равен нулю, led[0] равен единице, и наоборот. При этом все изменения происходят по фронту тактового сигнала. Похоже, что программа работает корректно. Ну и на ассертах ничего не свалилось, что как бы намекает.

Архив с описанным выше проектом можно скачать здесь. В качестве дополнительных источников информации я бы рекомендовал следующие:

- Если вас интересуют подробности по железу, обратите внимание на даташит Artix-7 [PDF], reference manual к Arty Artix-7 [PDF], а также схему платы [PDF];

- Книга Цифровая схемотехника и архитектура компьютера (Digital Design and Computer Architecture) — прекрасная книга, в которой, помимо прочего, подробно объясняются языки SystemVerilog и VHDL, а также внутреннее устройство FPGA;

- OpenCores.org — каталог всевозможных открытых проектов под FPGA. Для скачивания исходного кода требуется регистрация. Активация аккаунта производится модераторами вручную, поэтому может занимать несколько дней;

А пишите ли вы под FPGA? Если да, то на каком языке и какого производителя предпочитаете?

Вы можете прислать свой комментарий мне на почту, или воспользоваться комментариями в Telegram-группе.

Источник: eax.me

Программирование ПЛИС: Определение, языки и принцип работы

Архитектура аппаратного обеспечения — это дисциплина, которая включает в себя проектирование и создание физических компьютерных схем, выполняющих конкретные задачи, такие как шифрование кода или обработка пакетов. ПЛИС, или полевая программируемая вентильная матрица, — это форма аппаратной архитектуры, которая дает пользователям возможность настраивать схемы в любом месте и в любое время. Если вы заинтересованы в карьере в области технологий или компьютерных наук, изучение ПЛИС и способов их программирования поможет вам укрепить свои технические знания и навыки.

В этой статье мы рассказали о ПЛИС и их применении, описали программирование ПЛИС и то, как оно работает, а также перечислили языки, которые можно использовать для программирования ПЛИС.

Что такое ПЛИС?

ПЛИС — это интегральная схема, которую пользователи могут модифицировать для выполнения конкретных вычислительных задач даже после завершения процесса производства. Массив вентилей — это кремниевый чип с транзисторами, не имеющий заранее назначенной функции, что делает FPGA очень настраиваемой схемой, которую пользователи могут модифицировать в соответствии с потребностями своих уникальных проектов. ПЛИС программируется в полевых условиях, поскольку пользователи имеют возможность изменять функции схемы в любом месте и в любое время в соответствии со своими конкретными проектными намерениями.

ПЛИС имеют множество затворов, которые пользователи могут переконфигурировать для создания индивидуальных цифровых схем. Некоторые затворы внутри ПЛИС включают контроллеры памяти и коммуникационные интерфейсы, которые пользователи могут подключать для создания уникальных схем, отвечающих их конкретным технологическим потребностям. Этот процесс проектирования и курирования структур схемы является основной задачей архитектуры аппаратного обеспечения.

Приложения ПЛИС

ПЛИС — это гибкий массив вентилей, что часто делает ее привлекательной для разработчиков в различных областях технологической индустрии. Их основная цель — разработка интегральных схем для конкретных приложений, иначе известных как ASICs. Пользователи сначала проектируют схему, которая им нужна, в зависимости от обстоятельств и требований их задачи.

После того, как пользователи разработали и протестировали свою уникальную схему, они могут производить ASIC с этой схемой и экономить ценное время и деньги, которые в противном случае ушли бы на планирование и реализацию интегральной схемы. Одна ПЛИС может служить моделью для различных других проектов.

ПЛИС также играют важную роль в проектах, где схемы требуют корректировки. Если аппаратная конфигурация задания должна измениться в силу внешних обстоятельств, пользователь может легко и эффективно внести изменения в схему, чтобы лучше соответствовать потребностям проекта. Некоторые другие распространенные области применения ПЛИС включают:

- Искусственный интеллект

- Военные и космические проекты

- Медицинские инструменты

- Научные приборы

- Промышленные приборы

- Обработка пакетов

- Криптография, которая относится к процессу разгадывания кода

Что такое программирование ПЛИС?

Программирование ПЛИС — это процесс создания вычислительных решений с использованием ПЛИС. Процедуры разработки включают в себя планирование, проектирование и выполнение архитектуры затворов таким образом, чтобы получившаяся схема была функциональной и отвечала потребностям разработчиков. Конечной целью программирования ПЛИС является создание аппаратной схемы, которая при подаче питания генерирует определенные выходные сигналы. Почти все ПЛИС используют при программировании языки описания аппаратуры, или HDL.

Выделение времени на программирование ПЛИС может быть очень полезным для определения процессов, схем и потенциальных ошибок, которые могут возникнуть при работе аппаратуры. Вот почему важно тщательно планировать проектирование схем и сокращать любые потенциальные временные затраты. Это может включать отладку и изменение конфигурации аппаратной архитектуры, если первый план окажется нефункциональным.

Как работает программирование ПЛИС?

При программировании ПЛИС используются языки HDL для манипулирования схемами на основе желаемых возможностей устройства. HDL переводят коды на свой язык с помощью слов и символов, которые программное обеспечение для разработки может затем преобразовать в данные, загружаемые в ПЛИС. Это дает ей необходимые функции для выполнения требуемых задач ПЛИС.

Программирование ПЛИС схоже с программированием программного обеспечения, поскольку и то, и другое требует написания кода, который становится двоичным файлом. Разница, однако, заключается в том, что программирование программного обеспечения оптимизирует устройство для выполнения программы, в то время как программирование ПЛИС вносит физические изменения в аппаратное обеспечение. Изучение обоих навыков программирования может помочь вам преуспеть в сложной, технической роли.

Типы языков программирования ПЛИС

Вот несколько распространенных типов языков программирования ПЛИС, которые можно использовать для выполнения проектов по программированию ПЛИС:

VHDL

Язык описания аппаратуры очень высокоскоростных интегральных схем, или VHDL, — это язык, который можно использовать для конфигурирования электронной автоматики с конкретными конструкциями, определяющими выход схемы. VHDL описывает аппаратное обеспечение ПЛИС и позволяет пользователям моделировать и симулировать его до кодирования в реальное оборудование.

Это может быть хорошим инструментом для определения потенциальных ошибок в схеме, которые пользователи могут исправить до окончательного кодирования. VHDL имеет систему полного типа, что означает, что у пользователей есть возможность писать свой собственный структурированный код.

Verilog

Verilog — еще один распространенный HDL, который можно использовать при моделировании электронного оборудования при описании электронных систем. Verilog требует меньшего количества строк кода, и люди в технологической отрасли часто сравнивают его с языком кодирования программного обеспечения C.

Хотя некоторые считают Verilog более функциональным выбором для архитектуры аппаратного обеспечения. Это связано с тем, что многие сотрудники в области информатики и программирования считают Verilog одним из самых простых HDL для изучения при сохранении функциональности.

SystemVerilog

SystemVerilog возник как расширение Verilog и является одновременно языком описания аппаратуры и верификации аппаратуры. Как и другие HDL, вы можете использовать его для описания аппаратных схем, которые затем можно преобразовать в цифровой код и загрузить его в ПЛИС для выполнения конкретных задач.

SystemVerilog создает статические данные, которые не меняются в течение жизни программы, и автоматические данные, которые система генерирует в процессе разработки и выполнения программы. Ключевое различие между Verilog и SystemVerilog заключается в том, что первый моделирует электронные системы, а второй моделирует, проектирует и тестирует эти системы.

Ключевые слова:

- indeed.com

Источник: hr-portal.ru