Важнейшая роль в реализации сложных режимов работы отводится системе прерывания программ.

Прерывание — это приостанов выполнения программы в процессоре с целью выполнения какой-то более важной или нужной в данный момент другой программы или процедуры, после завершения которой продолжается выполнение прерванной программы с момента ее прерывания. Прерывание позволяет компьютеру приостановить любое свое действие и временно переключиться на другое, как заранее запланированное, так и неожиданное, вызванное непредсказуемой ситуацией в работе машины или ее компонента. Каждое прерывание влечет за собой загрузку определенной программы, предназначенной для обработки возникшей ситуации — программы обработки прерывания.

Организация и управление прерываниями функционально во многом смыкается с управлением задачами — одной из базовых функций операционных систем. Основой для управления процессом одновременного решения нескольких задач (равно как и управления прерываниями) являются процедуры:

Урок 14. Прерывания в компьютере

- выбора очередной задачи или определения приоритета задачи;

- сохранения информации о статусе задачи при ее прерывании (формирование слова состояния программы);

- упреждения и устранения конфликтов между задачами (координации и синхронизации выполнения задач).

Последовательность действий процессора при реализации прерывания такова. При появлении запроса на прерывание, запланированное заранее или неожиданное, процессор, как правило, после завершения выполнения текущей команды программы анализирует допустимость (разрешенность и приоритетность) данного вида прерывания. Если оно разрешено, процессор производит следующие действия:

- запоминает в стековой памяти текущее состояние прерываемой программы (состояние некоторых регистров МПП, в частности регистров F, CS, IP, а в микропроцессорах МП80286 и выше — и слова состояния программы, хранящегося в другом регистре МПП);

- посылает источнику запроса на прерывание запрос о причине (коде) прерывания;

- анализирует код запрошенного прерывания (номер прерывания — Ni) и формирует адрес ячейки (AV), хранящей вектор прерывания (вектор-адрес программы обработки прерывания) по формуле AV = 4·Ni (векторы прерываний занимают начальную 1024-байтовую область ОП с адресами ячеек от 00000 до 00400h (шестнадцатеричный код) так, что адрес вектора вычисляется простым умножением номера прерывания на четыре, так как CS и IP занимают по 2 байта каждый);

- считывает из ОП и записывает в регистры МПП (в регистры F, CS, IP ) вектор прерывания и его атрибуты;

- сбрасывает (устанавливает в 0) флаги прерывания (IF) и трассировки (TF);

- выполняет программу обработки прерывания (которую иногда называют драйвером прерывания);

- после выполнения программы обработки прерывания возвращает из стековой памяти параметры прерванной программы в регистры МПП и восстанавливает процесс выполнения прерванной программы.

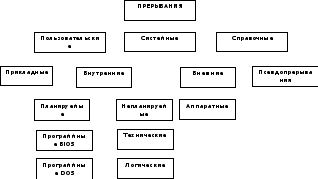

Видов (номеров) прерывания может быть всего 256, и, соответственно, векторов прерывания (адресов CS:IP программ обработки прерываний) в ОП насчитывается до 256. Классификация видов прерываний показана на рис. 18.4.

- базовой системы ввода-вывода — прерывания BIOS;

- операционной системы — прерывания DOS.

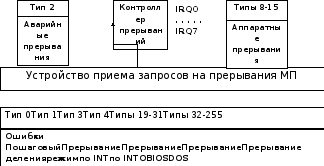

Программы обработки прерываний DOS, в отличие от программ обработки прерываний BIOS, не встроены в ПЗУ и для разных операционных систем могут быть разными. К программным прерываниям можно отнести также прерывания при пошаговом исполнении программы, при работе с контрольным остановом и т.д. Технические прерывания (или, иначе, прерывания от схем контроля) возникают при появлении отказов и сбоев в работе технических средств ПК. Большинство технических прерываний не маскируются, то есть они разрешаются всегда, а некоторые из них относятся к категории «аварийных» (например, отключение питания), и при их возникновении даже не запрашивается причина прерывания, а просто, по возможности, спасаются важные промежуточные результаты — записываются в безопасное место, в НЖМД, например. Логические прерывания возникают при появлении ошибок в выполняемых программах (деление на 0, потеря точности мантиссы, нарушение защиты памяти и т. п.). Многие из логических прерываний также относятся к категории немаскируемых. Прерывания обслуживаются базовой системой ввода-вывода — модулем расширения BIOS и модулем обработки прерываний DOS. BIOS и блок расширения BIOS имеют дело в основном с не планируемыми техническими и логическими прерываниями, пользовательскими прикладными прерываниями, а также со многими планируемыми прерываниями, обслуживающими систему ввода-вывода, детализированными и не очень детализированными (прерывания, обслуживаемые BIOS, часто называют прерываниями нижнего уровня). Модуль обработки прерываний DOS обслуживает в большинстве планируемые прерывания, в том числе и прерывания системы ввода-вывода. Прерывания DOS часто называют прерываниями верхнего уровня, так как, с одной стороны, в этих прерываниях меньше учитываются технические особенности элементов ПК, с другой стороны, при обработке этих прерываний часто случаются обращения к программам прерываний системы BIOS. Большинство прерываний BIOS имеют близкие аналоги среди прерываний DOS. Следует сказать, что использование прерываний BIOS позволяет, как правило, более детализировано выполнить обращения к различным системным ресурсам ПК, к элементам информационных структур и их атрибутам. Однако прерывания DOS более просты в использовании при программировании. Поэтому начинающим программистам можно рекомендовать работать с прерываниями DOS, особенно с расширенными функциями DOS для работы с файлами. Схема организации приема запросов на прерывания показана на рис. 18.5.  Рис. 18.5. Организация приема запросов на прерывания Для приема внешних прерываний имеются порты двух типов: NMI (None Masked Interrupt) для приема немаскируемых прерываний и INTR (Interrupt) — для приема прочих прерываний (INTR обычно используется для подсоединения контроллера прерываний). Если запрос на прерывание поступает по входу NMI, то прерывание не маскируется (имеет абсолютный приоритет) и сразу выполняется; по входу INTR прерывание разрешается, если в регистре флагов МПП флаг IF = 1. Всего предусмотрено 256 типов (0–255) прерываний. Из них только первые 5 жестко закреплены в МП, остальные используются системами BIOS и DOS.

Рис. 18.5. Организация приема запросов на прерывания Для приема внешних прерываний имеются порты двух типов: NMI (None Masked Interrupt) для приема немаскируемых прерываний и INTR (Interrupt) — для приема прочих прерываний (INTR обычно используется для подсоединения контроллера прерываний). Если запрос на прерывание поступает по входу NMI, то прерывание не маскируется (имеет абсолютный приоритет) и сразу выполняется; по входу INTR прерывание разрешается, если в регистре флагов МПП флаг IF = 1. Всего предусмотрено 256 типов (0–255) прерываний. Из них только первые 5 жестко закреплены в МП, остальные используются системами BIOS и DOS.

- Тип 0 — прерывание возникает при делении на 0 или если частное от деления переполняет разрядную сетку МП.

- Тип 1 — в режиме «трассировка» (при TF = 1) после выполнения каждой команды программы происходит останов.

- Тип 2 — немаскируемое техническое прерывание.

- Тип 3 — прерывание по команде INT, включенной в программу: останов и отображение содержимого регистров МПП.

- Тип 4 — прерывание по команде INTO, включенной в программу, но только если при выполнении предыдущей команды произошло переполнение разрядной сетки.

- Типы 8–15 — аппаратные прерывания, инициируемые внешними устройствами, поступают на входы IRQ0–IRQ7 контроллера прерываний (вход IRQ0 имеет высший приоритет, и прерывание, поступившее по этому входу, обрабатывается первым; всего уровней приоритета 8 и вход IRQ7 имеет низший приоритет).

- Типы 16–31 — планируемые программные прерывания BIOS.

- Типы 32–255 — программные прерывания DOS (жестко задействовано около 10, а вообще в разных версиях DOS их разное количество).

Прерывания с 0 по 31 и прерывание 64 относятся к прерываниям нижнего уровня, обслуживаемым BIOS; прерывания, начиная с 32 — являются прерываниями верхнего уровня (за исключением прерывания 64); причем прерывание 33 (21h) — это комплексное, чаще всего используемое в программах пользователя прерывание, имеющее около 100 разновидностей (служебных функций DOS). В некоторых типах прерываний BIOS и DOS имеется много разных функций , иногда более 10. Так, прерывание 10 (Ah) включает 15 функций, прерывание 33 (21h) — около 100 функций: в DOS 1.0 — 47, в DOS 2.0 — 88, в DOS 3.0 и выше — 99 функций (вид функции в рамках каждого прерывания определяется содержимым регистра AH). В работе [8] приведен список прерываний нижнего и верхнего уровня, а также служебных функций DOS наиболее часто используемого программистами прерывания 21h.

Системные прерывания грузят процессор? Разгрузи проц и дай ПК нормально работать!

Источник: studfile.net

Прерывания в конвейеризированных процессорах

Наверняка вы знаете, что такое прерывания. Возможно, даже интересовались устройством процессора. Почти наверняка вы нигде не видели внятный рассказ про то, как именно процессор обнаруживает прерывание, переходит к обработчику и, самое главное, возвращается из него именно туда, куда положено.

Я писал эту статью год. Изначально она была рассчитана на хардварщиков. Понимание того, что я ее никогда не закончу, а также жажда славы и желание, чтобы ее прочло больше десяти человек, заставило меня адаптировать ее для относительно широкой аудитории, повыкидывав схемы, куски кода на Верилоге и километры временных диаграмм.

Если когда-нибудь вы задумывались над тем, что значат слова «the processor supports precise aborts» в даташите, прошу под кат.

Немного терминологии: процессор, процессы и прерывания

- Процессоры с экзотическими архитектурами (стековыми, потоковыми, асинхронными и так далее), потому что их доля на рынке весьма мала, а в качестве примера логичнее использовать распространенную архитектуру. RISC я выбрал исключительно по религиозным соображениям

- Многоядерные процессоры, потому что каждое процессорное ядро обрабатывает свои прерывания независимо от других ядер

- Суперскалярные, многопоточные и VLIW процессоры, потому что с точки зрения организации прерываний они похожи на скалярные процессоры (хотя, разумеется, гораздо сложнее).

- Выборка команды из памяти

- Декодирование команды

- Исполнение команды

- Запись результатов в регистры и/или память

Процессор с параллельным выполнением команд может выполнять несколько команд одновременно. Например, процессор с четырехстадийным конвейером команд может одновременно записывать результаты первой команды, испонять вторую, декодировать третью и выбирать из памяти четвертую.

- счетчика команд процессора (program counter, он же instruction pointer)

- регистров процессора (общего назначения, статусных, флагов и так далее)

- оперативной памяти

- арифметические и логические команды обновляют содержимое регистров и счетчика команд

- команды перехода обновляют содержимое счетчика команд и таблицы динамического предсказания переходов

- команды загрузки обновляют содержимое регистров, счетчика команд и кэш-памяти (при промахе кэша; если потребуется замещение линии кэша — то еще и оперативной памяти)

- команды сохранения обновляют содержимое оперативной памяти (или кэш-памяти) и счетчика команд

- Внутренним, если вызвано выполнением команды в процессоре:

- Программным (software interrupt), если вызвано специальной командой

- Исключением (exception, fault, abort – это все оно), если вызвано ошибкой при выполнении команды

- Внешним, если вызвано произошедшим снаружи процессора событием

- процессор сохраняет счетчик команд в специальный регистр адреса возврата (РАВ), одновременно записывая вектор прерывания в счетчик команд, запуская таким образом обработчик прерывания

- все прочие элементы состояния процесса сохраняются обработчиком прерывания при необходимости (например, прежде чем использовать регистры, он должен сохранить их содержимое в стек)

- перед завершением обработчика прерывания он должен восстановить все элементы состояния процесса, которые изменял (например, восстановить содержимое регистров, сохраненное в стек)

- обработчик прерывания завершается командой возврата из прерывания, которая записывает содержимое РАВ обратно в счетчик команд, то есть возвращает управление прерванному процессу

Точные и неточные прерывания

- все команды, предшествующие прерываемой, были полностью выполнены и корректно сохранили состояние процесса

- все команды, следующие за прерываемой, не были выполнены и ни коим образом не изменили состояние процесса

- прерываемая команда, в зависимости от типа прерывания, либо была полностью выполнена, либо не была выполнена вовсе

- Команда, выполнявшаяся в момент прихода внешнего прерывания, должна обновить состояние процесса перед тем, как оно будет сохранено. То же самое касается команды, вызвавшей программное прерывание. В обоих случаях РАВ будет указывать на команду, которая, не случись прерывания, должна была быть выполнена следующей. Она и будет выполнена сразу после возврата из обработчика прерывания

- Команда, вызвавшая исключение — «плохая» команда. Ее результаты, скорее всего, некорректны, поэтому она не должна обновлять состояние процесса. Вместо этого в РАВ сохраняется ее адрес, после чего вызывается обработчик прерывания, который попытается исправить ошибку. После возврата из обработчика эта команда будет выполнена повторно. Если она снова вызовет такое же исключение, значит ошибка неисправима и процессор сгенерирует фатальное прерывание

Программные прерывания и исключения могут быть точными или неточными. В некоторых случаях без точных исключений просто не обойтись — например, если в процессоре есть MMU (тогда, если случается промах TLB, управление передается соответствующему обработчику исключения, который программно добавляет нужную страницу в TLB, после чего должна быть возможность заново выполнить команду, вызвавшую промах).

В микроконтроллерах исключения могут быть неточными. Например, если команда сохранения вызвала исключение из-за ошибки памяти, то вместо того, чтобы пытаться как-то исправить ошибку и повторно выполнить эту команду, можно просто перезагрузить микроконтроллер и начать выполнять программу заново (то есть сделать то же самое, что делает сторожевой таймер, когда программа зависла).

В большинстве учебников по архитектуре компьютеров (включая классику типа PattersonPatterson) точные прерывания обходятся стороной. Кроме того, неточные прерывания не представляют никакого интереса. По-моему, это отличные причины продолжить рассказ именно про точные прерывания.

Точные прерывания в процессорах с последовательным выполнением команд

Для процессоров с последовательным выполнением команд реализация точных прерываний довольно проста, поэтому представляется логичным начать с нее. Поскольку в каждый момент времени выполняется только одна команда, то в момент обнаружения прерывания все команды, предшествующие прерываемой, уже выполнены, а последующие даже не начаты.

Таким образом, для реализации точных прерываний в таких процессорах достаточно убедиться, что прерываемая команда никогда не обновляет состояние процесса до тех пор, пока не станет ясно, вызвала она исключение или нет.

Место, где процессор должен определить, позволить ли команде обновить состояние процесса или нет, называется точкой фиксации результатов (commit point). Если процессор сохраняет результаты команды, то есть команда не вызвала исключение, то говорят, что эта команда зафиксирована (на сленге — закоммичена).

- Выборка команды из памяти

- Декодирование команды

- Исполнение команды

- Запись результатов в регистры и/или память

- ошибка памяти при выборке команды

- неизвестный код операции при декодировании

- деление на ноль при исполнении

- ошибка памяти при записи результатов

- нельзя фиксировать команду и разрешать ей записывать результаты в память до тех пор, пока не станет ясно, что команда не вызвала исключение

- нельзя узнать, что исключение не вызвано, не записав результаты в память (для этого нужно получить подтверждение от контроллера памяти, что запись произведена успешно)

Как можно догадаться, эту проблему довольно сложно решить, поэтому во многих процессорах для простоты реализованы «почти точные» прерывания, то есть точными сделаны все прерывания, кроме исключений, вызванных ошибками памяти при записи результатов. В этом случае точка фиксации результатов находится между третьим и четвертым этапами цикла команды.

Важно! Нужно помнить, что счетчик команд тоже должен обновляться строго после точки фиксации результатов. При этом он изменяется вне зависимости от того, зафиксирована команда или нет — в него записывается либо адрес следующей команды, либо вектор прерывания, либо РАВ.

Точные прерывания в процессорах с параллельным выполнением команд

На сегодняшний день процессоров с последовательным выполнением команд почти не осталось (могу вспомнить разве что аналоги интеловского 8051) — их вытеснили процессоры с параллельным выполнением команд, обеспечивающие при прочих равных более высокую производительность. Простейший процессор с параллельным выполнением команд — процессор с конвейером команд (instruction pipeline).

Несмотря на многочисленные преимущества, конвейер команд значительно усложняет реализацию точных прерываний, чем много десятков лет печалит разработчиков.

В процессоре с последовательным выполнением команд этапы цикла команды зависят друг от друга. Простейший пример — счетчик команд. Вначале он используется на этапе выборки (как адрес в памяти, откуда должна быть прочитана команда), затем на этапе исполнения (для вычисления его следующего значения), и потом, если команда зафиксирована, он обновляется на этапе записи результатов. Это приводит к тому, что нельзя выбрать следующую команду до тех пор, пока предыдущая не завершит последний этап и не обновит счетчик команд. То же самое относится и ко всем прочим сигналам внутри процессора.

Процессор с конвейером команд можно получить из процессора с последовательным выполнением команд, если сделать так, чтобы каждый этап цикла команды был независим от предыдущих и последующих этапов.

- Результат выборки — закодированная команда — сохраняется в регистре, расположенном между этапами выборки и декодирования

- Результат декодирования — тип операции, значения операндов, адрес результата — сохраняются в регистрах между этапами декодирования и исполнения

- Результаты исполнения — новое значение счетчика команд для условного перехода, вычисленный в АЛУ результат арифметической операции и так далее — сохраняются в регистрах между этапами исполнения и записи результатов

- На последнем этапе результаты и так записываются в регистры и/или память, поэтому никакие вспомогательные регистры не нужны.

Такт СК Выборка Декодирование Исполнение Запись_результатов 1 0x00 Команда1 — — — 2 0x04 Команда2 Команда1 — — 3 0x08 Команда3 Команда2 Команда1 — 4 0x0C Команда4 Команда3 Команда2 Команда1 5 0x10 Команда5 Команда4 Команда3 Команда2

Обратите внимание на столбец СК («счетчик команд»). Его значение меняется каждый такт и определяет адрес в памяти, откуда выбирается команда.

Внимательный читатель уже заметил небольшую неувязочку — для обеспечения точности прерываний первая команда не имеет права изменить счетчик команд раньше четвертого такта. Чтобы это исправить, мы должны перенести счетчик команд за точку фиксации результата (предположим, что она находится между третьим и четвертым этапами):

Такт Выборка Декодирование Исполнение Запись_результатов СК 1 Команда1 — — — 0х00 2 — Команда1 — — 0х00 3 — — Команда1 — 0х00 4 Команда2 — — Команда1 0х04 5 — Команда2 — — 0х04

Производительность процессора немного упала, не так ли? На самом деле, решение лежит на поверхности – нам нужно два счетчика команд! Один должен находиться в начале конвейера и указывать, откуда читать команды, второй – в конце, и указывать на ту команду, которая должна быть зафиксирована следующей.

Первый называется «спекулятивным», второй – «архитектурным». Чаще всего спекулятивный счетчик команд не существует сам по себе, а встроен в предсказатель переходов. Выглядит это вот так:

Такт ССК Выборка Декодирование Исполнение Запись_результатов АСК 1 0x00 Команда1 — — — 0х00 2 0x04 Команда2 Команда1 — — 0х00 3 0x08 Команда3 Команда2 Команда1 — 0х00 4 0x0C Команда4 Команда3 Команда2 Команда1 0х04 5 0x10 Команда5 Команда4 Команда3 Команда2 0х08

- Если пришло внешнее прерывание, команда коммитится, но адрес следующей команды записывается не в АСК, а в РАВ. В АСК записывается адрес вектора прерывания.

- Если возникло исключение, команда не коммитится, вместо этого в АСК записывается адрес вектора соответсвующего исключения, а адрес команды записывается в РАВ.

- Если адрес команды не равен АСК, она тоже не коммитится (об этом позже). Если адрес равен АСК и исключения не произошло – процессор фиксирует команду и обновляет АСК (записывает адрес перехода в случае команды ветвления или просто инкрементирует в случае другой команды)

Такт ССК Выборка Декодирование Исполнение Запись_результатов АСК 1 0x00 jump 0x1234 — — — 0х00 2 0x04 Команда2 jump 0x1234 — — 0х00 3 0x08 Команда3 Команда2 jump 0x1234 — 0х00 4 0x0C Команда4 Команда3 Команда2 jump 0x1234 0х1234 *** Для Команды2 на четвертом такте ее адрес (0х04) не равен АСК, потому что переход был предсказан неверно*** 5 0x1234 Команда666 — — — 0х1234 6 0x1238 Команда667 Команда666 — — 0х1234 7 0x1240 Команда668 Команда667 Команда666 — 0х1234 8 0x1244 Команда669 Команда668 Команда667 Команда666 0х1238

На этом все. Разумеется, показаный четырехстадийный конвейер прост до невозможности. На самом деле, некоторые команды могут исполняться более одного такта, и даже простой микроконтроллер умеет завершать их не в том порядке, в котором он запустил их на выполнение, при этом обеспечивая точность прерываний. Однако общий принцип организации прерываний, смею вас заверить, остается тем же.

Желающим усугубить взрыв мозга рекомендую ознакомиться с Implementation of precise interrupts in pipelined processors. Да-да, ваш новейший Интел Кор Ай Семь работает именно так, как описано в этой статье двадцатипятилетней давности. Добро пожаловать в восьмидесятые!

Источник: habr.com

Файл не найден

Запрашиваемый вами файл не найден. Возможно он был удален, перемещен или вы ошиблись в адресе страницы.

Вы можете попробывать вернуться назад или перейти на главную страницу сайта.

или попробуйте посмотреть на старой версии сайта, возможно страница которую вы искали находится там.

403874 Волгоградская обл., г. Камышин, ул. Ленина 6а

Информационное наполнение:

пресс–центр института

Информационное сопровождение:

информационный вычислительный центр

2601

Всего: 108120427

Образование

- Курсы дополнительного профессионального образования

- Высшее образование

- Среднее профессиональное образование

- Второе высшее образование

- Центр проведения демонстрационного экзамена

- Восстановление и перевод

- IT школа «Камышонок»

Об институте

- Структура

- Администрация

- Нормативные документы

- Электронные сервисы

- Виртуальная приемная

- Контактная информация

- История института

- Клуб выпускников

- СМИ о нас

- Институту 20 лет

- Институту 25 лет

- Фирменный стиль

Наука

- Национальный проект «Наука и университеты»

- Научные труды сотрудников

- Основные направления

- Каталог научных услуг

- Разработки учёных института

- Руководство НИС

- Конференции

- Нормативная база

- Полезные ссылки

- Студенческое научно-техническое общество

Источник: www.kti.ru